تقنية خيوط المعالجة الفائقة

تحتاج هذه المقالة إلى تهذيب لتتناسب مع دليل الأسلوب في ويكيبيديا. (سبتمبر 2011) |

خيوط المعالجة الفائقة (بالإنجليزية: Hyper-threading) المعروف رسميًا باسم تقنية خيوط المعالجة الفائقة أو تقنية HT والمختصر HTT أو HT، هو تنفيذ تعدد مؤشرات الترابط المتزامن (SMT) الخاص بشركة انتل والذي يستخدم لتحسين توازي العمليات الحسابية (القيام بمهام متعددة في وقت واحد) التي يتم إجراؤها على معالجات دقيقة x86. تم طرحه على معالجات خادم إكسون في فبراير 2002 وعلى معالجات بنتيوم 4 المكتبية في نوفمبر 2002.[1] منذ ذلك الحين، قامت شركة انتل بتضمين هذه التقنية في وحدات المعالجة المركزية من سلسلة إيتانيوم وAtom وCore 'i' وغيرها.[2]

وبالإضافة إلى طلب دعم تعدد مؤشرات الترابط المتزامن في نظام التشغيل، لا يمكن استخدام مؤشرات الترابط الفائقة بشكل صحيح إلا مع نظام تشغيل مُحسّن خصيصًا له.[3]

ظهور الـ HT

[عدل]طرحت شركة إنتل تقنية HT وذلك في عام 2002 في معالجات XEON.

المصطلح في اللغة العربية

[عدل]يمكن ترجمة اسم التقنية لتكون ( خيوط المعالجة الفائقة) أو التخييط والمقصود منها هو أن العملية التي يقوم بها المعالج على البرنامج في خيط تنفيذ متسلسل تبعاً لأوامر البرنامج.

مفهوم الـ HT وآلية عمله

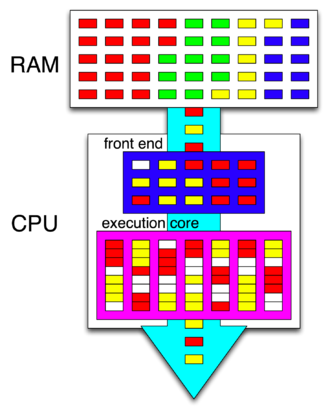

[عدل]نموذجياً، كل معالج طبيعي له حالة معمارية architectural state وحيدة على نواة معالج وحيد لخدمة خيوط المعالجة threads، تسمح تقنية HT لكل معالج فيزيائي (طبيعي) أن يملك بنيتين معماريتين على نواة واحدة (يقصد بالنواة الـ CPU الواحدة ضمن محفظة المعالج)، وأن يظهر كمعالجين منطقيين لخدمة خيوط المعالجة.

حيث يعد الـ BIOS كل بنية معمارية على المعالج الفيزيائي، ومنذ أن ظهرت هذه النظرية أخذت أنظمة التشغيل تستفيد من المعالجات المنطقية، وهذه الأنظمة امتلكت ضعف المصادر لخدمة خيوط المعالجة.

داخلياً، يملك المعالج المدعم بتقنية HT مجموعتين من السـّـِـجــِـلاّت ذات الأغراض العامة، general-purpose registers ، ومجموعتين من ســِـجــِـلاّت التنفيذ، ومجموعتين من بنى المكونات الأخرى، لكنه في المقابل يشترك المعالجان المنطقيّان في الذاكرة CACHE ووحدات التنفيذ والممرات، وأثناء المعالجة يتعامل كل معالج منطقي مع خيط معالجة منفرد، وهذا هو جوهر المعالج المدعّم بـ HT .

لتحقيق الهدف من تنفيذ خيطي معالجة على معالج فيزيائي واحد، يُبقي المعالج بشكل آني على سياق الخيوط المتعددة والتي تسمح للمؤقت بإرسال خيطين مستقلين بنفس الوقت.

يقوم نظام التشغيل بجدولة وإرسال خيوط الشيفرة thread of code simultaneous multithreading إلى كل معالج منطقي كما هو الحال في نظام المعالجة المتماثلة Symmetric Multiprocessing(SMP).

عندما لا يبعث خيط المعالجة، يستمر المعالج المنطقي في التسكّع، وعندما يحددّ خيط المعالجة ويُبعث إلى المعالج المنطقي LP0، تستعمل تقنية HT مصادر المعالج الضرورية لتنفيذ خيط المعالجة، وعندما يحدد خيط المعالجة الثاني ويُبعث إلى المعالج المنطقي الثاني LP1 تتضاعف المصادر أو تقسم أو ربما تصبح مشتركة عند الضرورة لتنفيذ خيط المعالجة الثاني.

يجعل كل معالج الخيارات في نقاط في طور الإعداد ليتحكم ويعالج الخيوط.

يجعل نظام التشغيل المعالج غير المستعمل في حالة تسكع، ويحرر المصادر للمعالج الذي يعمل. *(IBM SITE )* إذاً يقوم نظام التشغيل بتقديم التسهيلات للمعالج الذي يكون في حالة عمل ويجعل المعالج الأخر يدور في حلقة فارغة ريثما يحين دوره لأداء وظيفة قد تُطلب منه وبذلك يكون دور نظام التشغيل هو التنسيق ما بين المعالجين.

معالجات Intel وتقنية الـ HT

[عدل]قدمت Intel تقنية HT في خطّه من معالجات إنتل زيون للخادمات Servers في آذار 2002,وبذلك مكنت هذه التقنية الخادمات ذات المعالج المتعدد لتعمل بعدد مضاعف تماماً من المعالجات ولكن بشكل افتراضي، وكانت معالجات Xeonآنذاك بنظام ممرات MHZ533.

ثم وجدت هذه التقنية طريقها إلى معالجات الحواسيب الشخصية PC وتحديداً مع Pentium 43.06GHZ في الشهر العاشر من عام2002, كما ان HT موجودة في كل معالجاتentium 4 Super-threadingذات سرعة ممر Bus Speed 800MHZ .

وحتى في معالجات dual-core Pentium Extreme Edition .

مع ذلك يبقى المعالج Xeon هو الأول لتطبيق الربط الفائق الآني في معالجات الأغراض العامة.

المراجع

[عدل]- ^ "Intel Pentium 4 3.06GHz CPU with Hyper-Threading Technology: Killing Two Birds with a Stone." X-bit labs. مؤرشف من الأصل في 2014-05-31. اطلع عليه بتاريخ 2014-06-04.

- ^ "Intel® Hyper-Threading Technology (Intel® HT Technology)". Intel. مؤرشف من الأصل في 2024-04-16. اطلع عليه بتاريخ 2021-10-24.

- ^ Intel Required Components Interchangeability List for the Intel Pentium 4 Processor with HT Technology, includes list of Operating Systems that include optimizations for Hyper-Threading Technology; they are Windows XP Professional 64, Windows XP MCE, Windows XP Home, Windows XP Professional, some versions of Linux such as COSIX Linux 4.0, RedHat Linux 9 (Professional and Personal versions), RedFlag Linux Desktop 4.0 and SuSe Linux 8.2 (Professional and Personal versions) نسخة محفوظة 2012-07-18 at Archive.is