-

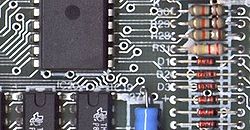

Plated-through holes on a multilayer board (magnified)

-

Double layered plating in CAD. Vias makes EDA placement possible.

Bottom layer – Red

Top layer – Blue -

Plating of plated-through holes:

Above – Top layer

Down – Bottom layer

ভিয়া (ইলেকট্রনিক্স)

এই নিবন্ধটিতে যদিও তথ্যসূত্রের একটি তালিকা, সম্পর্কিত পাঠ বা বহিঃসংযোগ রয়েছে, কিন্তু তা সত্ত্বেও এটির তথ্যসূত্রগুলি অস্পষ্ট, কারণ এটিতে নির্দিষ্ট বাক্য বা অনুচ্ছেদকে সমর্থনকারী অভ্যন্তরীণ তথ্যসূত্র প্রদান করা হয়নি। (সেপ্টেম্বর ২০২৪) |

১. গর্ত মাধ্যম

২. ব্লাইন্ড মাধ্যম

৩. সমাহিত মাধ্যম

ধূসর এবং সবুজ স্তরগুলো পরিবাহী নয়, অন্যদিকে, পাতলা কমলা স্তর এবং লাল ভায়াগুলি পরিবাহী।

ভিয়া (via) (ল্যাটিন ভাষায় 'পথ' বা 'পন্থা') হল একটি বৈদ্যুতিক সংযোগ যা প্রিন্টেড সার্কিট বোর্ড (PCB) বা ইন্টিগ্রেটেড সার্কিটের দুটি বা তার বেশি ধাতব স্তরের মধ্যে সংযোগ স্থাপন করে। মূলত, একটি ভিয়া একটি ছোট ছিদ্র করা গর্ত যা দুটি বা তার বেশি সংলগ্ন স্তরের মধ্যে দিয়ে যায়; গর্তটি ধাতু (সাধারণত তামা) দিয়ে প্রলেপ দেওয়া হয় যা অন্তরক স্তরগুলির মধ্য দিয়ে বৈদ্যুতিক সংযোগ তৈরি করে।

পিসিবি উৎপাদনে ভিয়া (vias) একটি গুরুত্বপূর্ণ বিষয়। যেহেতু উল্লম্ব কাঠামো এগুলি একাধিক স্তর অতিক্রম করে, সেগুলি বেশিরভাগ ডিজাইনের থেকে আলাদাভাবে নির্দিষ্ট করা হয়, যা ত্রুটির সম্ভাবনা বাড়ায়। এগুলি অন্যান্য বৈশিষ্ট্যগুলির তুলনায় ভিন্ন সরঞ্জাম দিয়ে তৈরি করা হয়—যা সাধারণত শিথিল সহনশীলতা (looser tolerances) সহ থাকে। যদি গর্ত বা কোনো স্তর সামান্য হলেও স্থানচ্যুত হয়, তাহলে ভুল বৈদ্যুতিক সংযোগ তৈরি হতে পারে; এটি পৃষ্ঠ থেকে দৃশ্যমান নাও হতে পারে। গর্তটি ড্রিল করার পরে, এটি অবশ্যই পরিবাহী উপাদান দিয়ে রেখাযুক্ত (lined) করতে হবে, কপার স্তরে শুধুমাত্র পরিবাহী উপাদান রেখে দেওয়ার বিপরীতে। এমনকি একটি প্রাথমিকভাবে ভাল বোর্ডও পরে সমস্যা তৈরি করতে পারে কারণ ভিয়া এর চারপাশের স্তরের চেয়ে ভিন্নভাবে তাপে প্রতিক্রিয়া দেখায়। ভিয়াগুলি বৈদ্যুতিক প্রতিবন্ধকতার একটি বিচ্ছিন্নতার প্রতিনিধিত্ব করে, যা সংকেত অখণ্ডতার জন্য সমস্যা সৃষ্টি করতে পারে।

প্রিন্টেড সার্কিট বোর্ডের মধ্যে ভিয়ার ব্যবহার

[সম্পাদনা]

প্রিন্টেড সার্কিট বোর্ড (PCB) ডিজাইনে, ভিয়া (via) দুটি প্যাড নিয়ে গঠিত যা বোর্ডের বিভিন্ন কপার স্তরে একই অবস্থানে থাকে এবং একটি গর্তের মাধ্যমে বৈদ্যুতিকভাবে সংযুক্ত থাকে। ছিদ্রটিকে ইলেক্ট্রোপ্লেটিং দ্বারা পরিবাহী করা হয়, বা একটি নল বা একটি রিভেট দিয়ে রেখাযুক্ত করা হয়। উচ্চ-ঘনত্বের মাল্টিলেয়ার পিসিবি-তে মাইক্রোভিয়াস থাকতে পারে: ব্লাইন্ড ভিয়া (blind vias) বোর্ডের শুধুমাত্র একপাশে উন্মুক্ত থাকে, যখন সমাহিত মাধ্যম (buried vias) অভ্যন্তরীণ স্তরগুলিকে সংযুক্ত করে কোনো পৃষ্ঠে উন্মুক্ত না হয়ে। তাপীয় ভিয়া (thermal vias) পাওয়ার ডিভাইস থেকে তাপ সরিয়ে নিয়ে যায় এবং সাধারণত প্রায় এক ডজনের একটি অ্যারে (array) হিসাবে ব্যবহৃত হয়। [১]

ভিয়া নিম্নের উপাদান দ্বারা গঠিত হয়:

- ব্যারেল — পরিবাহী নল ড্রিল করা গর্ত ভরাট করে

- প্যাড - ব্যারেলের প্রতিটি প্রান্তকে উপাদান, সমতল বা ট্রেসের সাথে সংযুক্ত করে

- অ্যান্টিপ্যাড - ব্যারেল এবং ধাতব স্তরের মধ্যে ক্লিয়ারেন্স গর্ত যার সাথে এটি সংযুক্ত নয়

কিছু ভিয়া (via), যাকে কখনও কখনও PTV বা প্লেটেড-থ্রু-ভিয়া বলা হয়, এটি প্লেটেড-থ্রু-হোল (PTH) এর সাথে বিভ্রান্ত হওয়া উচিত নয়। একটি ভিয়া ব্যবহার করা হয় পিসিবি-এর কপার স্তরগুলির মধ্যে আন্তঃসংযোগ হিসাবে, যেখানে প্লেটেড-থ্রু-হোল সাধারণত ভিয়াগুলির চেয়ে বড় হয় এবং এটি একটি প্লেটেড হোল হিসাবে ব্যবহৃত হয় যা উপাদানগুলির লিড বা ধাতব শীর্ষ গ্রহণ করে - যেমন নন-SMT রেজিস্টর, ক্যাপাসিটর এবং DIP প্যাকেজ আইসি। প্লেটেড-থ্রু-হোল মেকানিক্যাল সংযোগের জন্যও ব্যবহার করা যেতে পারে, যেখানে ভিয়া সাধারণত তা নয়। প্লেটেড-থ্রু-হোল-এর আরেকটি ব্যবহার হল ক্যাসটেলেটেড হোল, যেখানে প্লেটেড-থ্রু-হোল বোর্ডের প্রান্তে সারিবদ্ধ করা হয় যাতে প্যানেল থেকে বোর্ডটি মিল করার সময় এটি অর্ধেক কাটা হয় - এর প্রধান ব্যবহার হল একটি পিসিবি-কে অন্যটিতে স্ট্যাক করার জন্য সোল্ডার করার অনুমতি দেওয়া, যা একযোগে ফাস্টেনার এবং সংযোগকারী হিসাবে কাজ করে।

ডানদিকে দেখানো তিনটি প্রধান ধরনের ভিয়াস (vias) রয়েছে। একটি পিসিবিতৈরি করার মৌলিক ধাপগুলি হল: সাবস্ট্রেট উপাদান তৈরি করা এবং এটি স্তরে স্তরে সজ্জিত করা; ভিয়াসের থ্রু-ড্রিলিং এবং প্লেটিং; এবং ফটো-লিথোগ্রাফি এবং এচিং ব্যবহার করে কপার ট্রেস প্যাটার্নিং। এই স্ট্যান্ডার্ড পদ্ধতির সাথে, ভিয়ার সম্ভাব্য কনফিগারেশনগুলি থ্রু-হোল পর্যন্ত সীমাবদ্ধ থাকে। তবে, লেজার ব্যবহারের মতো গভীরতা-নিয়ন্ত্রিত ড্রিলিং প্রযুক্তি আরও বৈচিত্র্যময় ভিয়া প্রকারের জন্য অনুমতি দেয়। (লেজার ড্রিলগুলিও যান্ত্রিক ড্রিলের তুলনায় ছোট এবং আরও সঠিকভাবে অবস্থানকৃত গর্ত তৈরি করতে পারে।)

পিসিবি তৈরির প্রক্রিয়া সাধারণত একটি তথাকথিত কোর দিয়ে শুরু হয়, একটি মৌলিক ডাবল-সাইডেড পিসিবি। প্রথম দুটি স্তরের বাইরের স্তরগুলি এই মৌলিক বিল্ডিং ব্লক থেকে স্তরে স্তরে সজ্জিত হয়। যদি কোরের নীচের দিক থেকে দুটি স্তর একের পর এক সজ্জিত করা হয়, তাহলে 1-2 ভিয়া, 1-3 ভিয়া এবং একটি থ্রু-হোল থাকতে পারে। প্রতিটি স্ট্যাকিং পর্যায়ে ড্রিলিং করে প্রতিটি ধরণের ভিয়া তৈরি করা হয়। যদি কোরের উপরে একটি স্তর সজ্জিত করা হয় এবং অন্যটি নীচ থেকে সজ্জিত করা হয়, তবে সম্ভাব্য ভিয়া কনফিগারেশনগুলি হল 1-3, 2-3 এবং থ্রু-হোল। ব্যবহারকারীর জন্য প্রয়োজনীয় যে, পিসিবি প্রস্তুতকারকের অনুমোদিত স্ট্যাকিং পদ্ধতি এবং সম্ভাব্য ভিয়াস সম্পর্কে তথ্য সংগ্রহ করতে হবে। সস্তার বোর্ডগুলির জন্য, শুধুমাত্র থ্রু-হোল তৈরি করা হয় এবং ভিয়াসের সাথে সংযুক্ত না হওয়ার জন্য আন্টিপ্যাড (বা ক্লিয়ারেন্স) স্তরগুলিতে স্থাপন করা হয়।

যদি পিসিবির ভিয়াগুলি ভালোভাবে তৈরি করা হয়, তবে ভিয়াগুলি প্রধানত Z-অক্ষ বরাবর কপার প্লেটিং এবং পিসিবির মধ্যে পার্থক্যমূলক সম্প্রসারণ এবং সংকোচনের কারণে ব্যর্থ হবে। এই পার্থক্যমূলক সম্প্রসারণ এবং সংকোচন কপার প্লেটিংয়ে চক্রাকার ক্লান্তি (cyclic fatigue) সৃষ্টি করবে, যা শেষ পর্যন্ত ক্র্যাক প্রসারণ এবং একটি বৈদ্যুতিক খোলা সার্কিট (open circuit) সৃষ্টি করবে। বিভিন্ন ডিজাইন, উপাদান, এবং পরিবেশগত পরামিতি এই অবক্ষয়ের গতিকে প্রভাবিত করবে।

ভিয়ার স্থায়িত্ব নিশ্চিত করতে, IPC একটি একটি ব্যর্থতা সময়কাল গণক (time to failure calculator) তৈরি করেছে।

ইন্টিগ্রেটেড সার্কিট মধ্যে ভিয়ার ব্যবহার

[সম্পাদনা]ইন্টিগ্রেটেড সার্কিট (IC) ডিজাইনে, ভিয়া হল একটি ছোট খোলা স্থান যা একটি ইনসুলেটিং অক্সাইড স্তরে থাকে এবং বিভিন্ন স্তরের মধ্যে একটি পরিবাহী সংযোগ তৈরি করতে ব্যবহৃত হয়। ইন্টিগ্রেটেড সার্কিটে একটি ভিয়া সম্পূর্ণভাবে একটি সিলিকন ওয়েফার বা ডাইয়ের মাধ্যমে অতিক্রম করে তাকে "থ্রু-চিপ ভিয়া" বা "থ্রু-সিলিকন ভিয়া" (TSV) বলা হয়। কর্নিং গ্লাস সেমিকন্ডাক্টর প্যাকেজিংয়ের জন্য থ্রু-গ্লাস ভিয়া (TGV) নিয়ে গবেষণা করেছে, কারণ সিলিকন প্যাকেজিংয়ের তুলনায় গ্লাস প্যাকেজিংয়ে বৈদ্যুতিক ক্ষতি কম হয়। সর্বনিম্ন স্তরের ধাতুকে ডিফিউশন বা পলির সাথে সংযুক্ত করা একটি ভিয়াকে সাধারণত "কন্টাক্ট" বলা হয়।

আরও পড়ুন

[সম্পাদনা]- "Tips for PCB Vias Design" (পিডিএফ) (Technical note)। Quick-teck। ২০১৪। EN-00417। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- "Via Tenting - Overview of the variations"। WE Online। Würth Elektronik GmbH & Co. KG। ২০১৪। Printed Circuit Boards > Layout > Design Tip > Tenting। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- "Via Plugging - Overview of the variations"। WE Online। Würth Elektronik GmbH & Co. KG। ২০১৪। Printed Circuit Boards > Layout > Design Tip > Plugging। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- "Via Filling - Overview of the variations"। WE Online। Würth Elektronik GmbH & Co. KG। ২০১৩। Printed Circuit Boards > Layout > Design Tip > Filling। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- "Microvia Filling"। WE Online। Würth Elektronik GmbH & Co. KG। ২০১৫। Printed Circuit Boards > Layout > Design Tip > Microvia Filling। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- Dingler, Klaus (২০০৯-০৩-১৮)। "Pluggen / Plugging"। FED-Wiki (জার্মান ভাষায়)। Fachverband Elektronik-Design e.V. (FED)। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- "Via Optimization Techniques for High-Speed Channel Designs" (পিডিএফ) (Application note)। Altera Corporation। মে ২০০৮। AN-529-1.0। ২০১৭-১২-১৮ তারিখে মূল (পিডিএফ) থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- Chu, Jun (২০১৭-০৪-১১)। "Controlled Depth Drilling, or Back Drilling"। Online Documentation for Altium Products। Altium। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- Loughhead, Phil (২০১৭-০৫-৩০)। "Removing Unused Pads and Adding Teardrops"। Online Documentation for Altium Products। Altium। ২০১৭-১২-১৮ তারিখে মূল থেকে আর্কাইভ করা। সংগ্রহের তারিখ ২০১৭-১২-১৮।

- Brooks, Douglas G.; Adam, Johannes (২০১৭-০২-০৯)। PCB Trace and Via Temperatures: The Complete Analysis (2nd সংস্করণ)। CreateSpace Independent Publishing Platform। আইএসবিএন 978-1541213524।

তথ্যসূত্র

[সম্পাদনা]- ↑ Gautam, Deepak; Wager, Dave (১৭ মার্চ ২০১৩)। A review of thermal management in power converters with thermal vias। IEEE। ডিওআই:10.1109/APEC.2013.6520276।