Intel 80386

| << Intel 80386 >> | |

|---|---|

Intel i386DX, 16 MHz | |

| Produktion: | 1985 bis 2007 |

| Produzenten: | |

| Prozessortakt: | 12 MHz bis 40 MHz |

| L1-Cachegröße: | 0 KiB |

| Fertigung: | 1,5 µm bis 1,0 µm, CMOS |

| Befehlssatz: | x86 bis IA-32 (16-/32-Bit) |

Sockel:

| |

Der 80386 (Markenbezeichnung i386, anfangs iAPX 386) ist ein x86-Prozessor mit 32-Bit-Architektur, der von Intel als Nachfolger des 80286 entwickelt und von 1985 bis September 2007 produziert wurde. Das 386er-Design wurde später von AMD in Lizenz gefertigt und die Prozessoren als Am386 verkauft; IBM lizenzierte den i386SX und entwickelte daraus den verbesserten IBM 386SLC. Mehrere Firmen entwickelten kompatible eigene Prozessoren, beispielsweise Chips & Technologies, Cyrix oder NexGen.

Geschichtliche Bedeutung

[Bearbeiten | Quelltext bearbeiten]Mit dem 80386 vollzog Intel auf der x86-Architektur, ursprünglich eine reine 16-Bit-Architektur, den Wechsel auf eine vollwertige 32-Bit-Architektur. Eingeführt als i386 wurde die 32-Bit-x86-Architektur von Intel retronym in „Intel Architecture, 32 Bit“, oder abgekürzt IA-32, umbenannt.[1] Die Funktionen des i386 sind auch in allen Nachfolgemodellen bis zur aktuellen Core-i-Generation[2] immer noch vorhanden. Gleichzeitig diente die Prozessorarchitektur IA-32 auch anderen Herstellern als Vorlage für eigene x86-Prozessoren. Die Register dieser Prozessorfamilie sowie der Adressraum der Architektur sind 32 Bit breit. Auf der Grundlage der i386-Architektur und späterer Erweiterungen (allen voran SSE) baut auch die von AMD um die Jahrtausendwende entwickelte 64-Bit-Erweiterung AMD64 auf.

Der 80386 wird weiterhin für Steuerungsaufgaben (z. B. in Telefonvermittlungsanlagen) sowie in der Luft- und Raumfahrt eingesetzt. Der Grund liegt darin, dass seine Rechenleistung für diese Aufgaben vollkommen ausreicht und er als vollständig durchgetestet gilt – das heißt, dass er allen denkbaren Situationen schon ausgesetzt war und daher mit keiner existierenden oder kommenden Software noch ein unvorhergesehenes Verhalten zu erwarten ist. Ein weiterer Grund ist seine hohe Resistenz gegen Strahlung.

Die Entwicklung bei Intel leitete ab 1982 John Crawford.

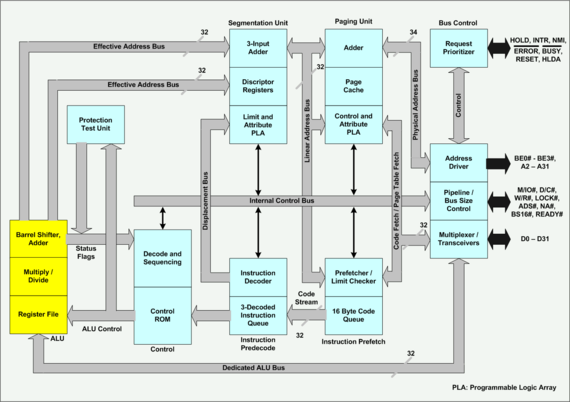

Architektur

[Bearbeiten | Quelltext bearbeiten]

Varianten

[Bearbeiten | Quelltext bearbeiten]Es gab insgesamt vier Varianten dieses Hauptprozessors, welche sich im Daten-Bus und im Einsatzzweck unterschieden. Die Produktion des i386EX als Embedded-Version des i386SX wurde erst im Jahr 2007 eingestellt.

Intel i386SX

Eine Variante des 80386 ist der 80386SX. Die Bezeichnung bedeutet Single-word eXternal. Er besitzt nur einen 16 Bit breiten externen Datenbus und einen 24 Bit breiten Adressbus, behält intern aber die 32-Bit-Mikroarchitektur des 80386 bei. Der 24 Bit breite Adressbus beschränkt den adressierbaren physischen Speicher des 80386SX zwar auf 16 MiB; angesichts eines zu Beginn der 1990er Jahre im Heimbereich üblichen Speicherausbaus von zumeist maximal 4 MiB war das aber keine gravierende Einschränkung, zumal viele für den 80386SX vorgesehenen Hauptplatinen einen Speicherausbau von 16 MiB auch nicht erlaubten. Aus Programmierersicht bestand, abgesehen von der Speicherlimitierung, praktisch kein Unterschied zwischen dem 80386SX und dem „echten“ 80386, der zur Unterscheidung von seinem kleinen Bruder nach dessen Einführung in 80386DX, bzw. i386DX (Double-word eXternal) umbenannt wurde. Aufgrund der verringerten Datenbusbreite und niedrigerer verfügbarer Taktraten erreicht der 80386SX gegenüber dem 80386DX nur eine deutlich geringere Ausführungsgeschwindigkeit.

80386SL

Der 80386SL (i386SL) ist eine Version des i386SX für tragbare Computer. Mit ihm wurde der System Management Mode (SMM) eingeführt, der zu Stromsparzwecken den Hauptprozessor in Tiefschlaf versetzen kann.

RapidCAD

Der RapidCAD war ein auf dem Intel 80486 basierendes Upgrade für 80386-Systeme. Der RapidCAD bestand aus zwei Chips, dem RapidCAD1 und dem RapidCAD2, wobei ersterer den 80386-Hauptprozessor und letzterer den 80387-Koprozessor ersetzte. Der RapidCAD2 enthielt aber keine Elektronik des Koprozessors, sondern lediglich eine Logik zur Erzeugung externer Bussignale. Der eigentliche Koprozessor befand sich schon im RapidCAD1 integriert.

Gegenüber einem i386-System mit i387-Coprozessor brachte der RapidCAD – je nach Anwendung – eine moderate Leistungssteigerung von ungefähr 30 Prozent; an ein System mit vollumfänglichem 80486-Prozessor reichte die Leistung aber nicht heran. Neben dem hohen Preis sorgte unter anderem dieser Umstand dafür, dass der RapidCAD keine weite Verbreitung erfuhr, weshalb die Chip-Kombination heute begehrtes Sammlerobjekt ist.

Segmente

[Bearbeiten | Quelltext bearbeiten]Der 80386 kann direkt bis zu 4 GiB Hauptspeicher adressieren (80386SX: 16 MiB). Der logische Adressraum beträgt 246 B = 64 TiB, welcher aber nur theoretisch vollständig nutzbar ist. Der Prozessor verwendet dabei im Protected Mode die segmentierte Speicheradressierung mit 16 Bit breiten Selektoren und – je nach Betriebsmodus – 16 oder 32 Bit breite Offsets.

Die Segmentierungseinheit unterstützt wie beim 80286 vier Privilegienstufen, bei Intel „Ringe“ genannt, die für folgende Aufgaben vorgesehen sind:

- Ring 0 – für den Kernel und Gerätetreiber

- Ring 1 – für Treiber, die keinen unbeschränkten Hardwarezugriff benötigen (z. B. Dateisystemtreiber), nur selten genutzt

- Ring 2 – für Systemdienste

- Ring 3 – für die Ausführung von normalen Anwendungen

Nur wenige PC-Betriebssysteme haben diese vier Privilegienstufen genutzt. Meist wurden (auch aufgrund der Kompatibilität zu anderen Prozessorarchitekturen, die nur zwei Privilegienstufen kennen) nur Ring 0 (für Kernel und Basis-Treiber) und Ring 3 (für allen übrigen Code) verwendet.

Bezüglich Sicherheit ist der Protected Mode dem flachen Adressiermodell, das sich nunmehr durchgesetzt hat, deutlich überlegen. Dennoch benutzen nahezu alle neueren PC-Betriebssysteme für Anwendungsprogramme ausschließlich das Flat-Memory-Modell. Dieses vereinfacht die Programmierung und ist auf andere Prozessorarchitekturen übertragbar, die keine Segmentierungseinheit besitzen.

Hardwareseitig ist auch die parallele Nutzung von Segmentierung und Paging möglich. Dabei wird zuerst durch die Segmentierung die lineare Adresse berechnet und dann über das Paging in die physische Adresse umgesetzt. Ohne Paging entspricht die lineare Adresse der physischen Adresse.

Bei Verwendung eines sogenannten Flat-Memory-Modells, bei dem Daten-, Code- und Stacksegment in einen linearen 4-GiB-Adressraum der Anwendungsprogramme eingeblendet werden, ist der Speicher innerhalb der Anwendungsprogramme über einfache 32-Bit-Offsets adressierbar. Damit wird der Speicherschutz, den die Segmentierungseinheit bietet, ausgehebelt. Im von AMD eingeführten long mode in 64-Bit-x86-Prozessoren wurde keine Erweiterung der Segmentierung vorgesehen, sodass bei x64 nur noch ein Flat-Memory-Modell nutzbar ist.

Die Paging-Einheit ermöglicht nur einen relativ einfachen, seitenbasierten Speicherschutz. Inzwischen wird versucht, den mit dem Flat-Memory-Modell verbundenen Sicherheitslücken durch neue Hardwareerweiterungen wie NX-Bit (ab dem Athlon 64) oder SMEP beizukommen.

Paging

[Bearbeiten | Quelltext bearbeiten]Zur Verwaltung dient nun eine zusätzliche Ebene, welche 4 KiB große Speicherseiten verwendet. Die Basisadressen aller Seiten werden in Seitentabellen verzeichnet. Diese werden in Seitenverzeichnissen zu 1024 Einträgen gespeichert. Ein Adressraum der Größe 4 GiB wird folglich in 1024 × 1024 Seiten zu 4 KiB aufgeteilt. So kann die lineare 32-Bit-Adresse in drei Bestandteile aufgeteilt werden:

- 12 Bit – Offset in der Speicherseite

- 10 Bit – Index auf Seitentabelle

- 10 Bit – Index auf Seitenverzeichnis

Auf der Seitenebene gibt es zwei Privilegstufen:

- Supervisor-Mode – für Betriebssystem und Treiber (Ring 0, 1 und 2)

- User-Mode – für Anwendungsprogramme (Ring 3)

In Klammern ist die Entsprechung der Segmentprivilegien angegeben.

Register

[Bearbeiten | Quelltext bearbeiten]Der i386 hat acht 32-Bit-Register. Sieben dieser Register hatten zwar teilweise spezielle Verwendungszwecke im Zusammenhang mit verschiedenen Befehlen, konnten aber ansonsten frei zum Rechnen und allgemeinen Datenaustausch verwendet werden:

| Abk. | Name | Spezielle Verwendung |

|---|---|---|

| EAX | Accumulator | niederwertiger Teil und erster Operand bei Multiplikation; Quotient bei Division; BCD-Befehle |

| EBX | Base Register | keine (Das 16-Bit-Register BX konnte im 16-Bit-Modus zur Index-Adressierung benutzt werden; im 32-Bit-Modus ist dies mit allen General-Purpose-Registern möglich.) |

| ECX | Count Register | Schleifenzähler für JCXZ und LOOP; Verschiebedistanz von Verschiebebefehlen |

| EDX | Data Register | höherwertiger Teil bei Multiplikation; Rest bei Division; Portadresse für die Befehle IN reg,DX und OUT DX,reg |

| EBP | Base Pointer | Wird zur Adressierung des Stapelspeichers für lokale Variablen/Parameterübergabe benutzt. |

| ESP | Stack Pointer | Zeiger auf die aktuelle Position im Stapelspeicher-Segment; nur sehr eingeschränkt allgemein verwendbar, da dieses Register angibt, wo die Rücksprungadresse von Unterprogrammen und Interrupts gespeichert wird. |

| ESI | Source Index | Quelle für Zeichenketten-Operationen |

| EDI | Destination Index | Ziel für Zeichenketten-Operationen |

Daneben gibt es auch noch weitere Register zur Steuerung des Verhaltens des Prozessors:

| Abk. | Name | Verwendung |

|---|---|---|

| EIP | Instruction Pointer | Zeigt auf den nächsten auszuführenden Befehl. |

| EFLAGS | Flag Register | Die einzelnen Bits besitzen unterschiedliche Bedeutungen und zeigen z. B. Überläufe bei arithmetischen Operationen u. ä. an. |

| CS | Code Segment | Segmentselektor des Codesegments (in dem der aktuell auszuführende Programmcode steht) |

| DS | Data Segment | Segmentselektor des Datensegments (in dem die globalen Daten des Programms stehen) |

| SS | Stack Segment | Segmentselektor des Stapelspeichersegments (in dem der Stapelspeicher für die lokalen Daten und Rücksprungadressen stehen) |

| ES | Extra Segment | Segmentselektor eines weiteren Datensegments (wird z. B. für Zeichenketten-Kopierbefehle verwendet) |

| FS und GS | Extra Segment 2 und 3 | Segmentselektoren zweier weiterer Datensegmente |

| GDTR | Global Descriptor Table Register | Speichert lineare Adresse und Größe der GDT |

| LDTR | Local Descriptor Table Register | Segmentselektor für das Segment, das die gerade aktive LDT enthält (Es können sich in der GDT zeitgleich mehrere LDT Einträge befinden) |

| IDTR | Interrupt Descriptor Table Register | Speichert die lineare Adresse und Größe der IDT |

| CR0...CR3 | Control Register 0...3 | Steuern u. A. das Paging, den Koprozessor und den Protected Mode (Untere 16 Bit des CR0 sind das vom 80286 übernommene MSW) |

| TR6...TR7 | Test Register 6...7 | Zum Überprüfen des Translation Lookaside Buffer. |

| DR0...DR7 | Debug Register 0...7 | Dienen zum Festlegen von vier Haltepunkten auf Prozessorebene (DR0...DR3) u. a. |

| TR | Task Register | Segmentselektor des aktiven Task Status Segments (TSS) (Es können sich zeitgleich mehrere TR in der GDT und LDT befinden) |

Alle General-Purpose-Register, sowie EIP und EFLAGS, sind auf 32 Bit erweiterte (das E kommt vom englischen extended) Versionen entsprechender 16-Bit-Register der Vorgänger 8086 bis 80286.

Prozessor-Bugs

[Bearbeiten | Quelltext bearbeiten]POPA/POPAD-Bug

[Bearbeiten | Quelltext bearbeiten]Dieser Fehler tritt bei allen i386ern auf. Wenn unmittelbar nach dem POPA- oder POPAD-Befehl ein Befehl folgt, bei dem eine Speicheradresse aus einem Basis- und Indexregister berechnet wird, ist der Wert im EAX-Register undefiniert. Wird als Basis- oder Indexregister beim Speicherzugriff EAX benutzt, bleibt der Prozessor hängen (nur POPA). Der Linux-Kernel führt beim Booten einen Test durch und gibt bei vorhandenem Fehler die Meldung Checking for popad bug... Buggy. aus, bootet anschließend aber weiter.

Überprüfung der Grenze des TSS

[Bearbeiten | Quelltext bearbeiten]Der Prozessor überprüft, ob die eingetragene Größe des Task Status Segments (TSS) groß genug ist. Die Ausnahme 10 wird immer dann ausgelöst, wenn das TSS kleiner als 101 Bytes ist, sollte aber eigentlich schon bei kleiner als 103 Bytes auslösen.

B1 Bug

[Bearbeiten | Quelltext bearbeiten]Dieser Fehler tritt nur beim B1 Stepping des i386 bei bestimmten Befehlsfolgen auf, die vermieden werden können, wenn zwischen den Befehlsfolgen ein anderer Befehl eingebaut wird, der das Triggern des Bugs verhindert. Microsoft versuchte anfangs bei Windows 95 Prozessoren mit diesem B1 Stepping zu unterstützen und entschied sich dann am Ende doch dagegen. Außerdem unterstützt das B1 Stepping keinen virtuellen Speicher in den ersten 64 KiB des Arbeitsspeicher.[3] Obwohl 386er CPUs noch über keinen CPUID-Befehl verfügen, kann das Stepping über eine gezielte Programmierung dennoch per Software ausgelesen werden.[4]

Modelldaten

[Bearbeiten | Quelltext bearbeiten]i386DX

[Bearbeiten | Quelltext bearbeiten]

- Prozessor-Cache: Cache befand sich zu diesen Zeiten auf der Hauptplatine, Prozessoren selbst hatten keinen Cache.

- Hauptplatinen-Cache: Üblich waren 64 kB direkt-gemappter Cache bei Prozessoren ab einer Taktrate von 33 MHz.[5]

- Bauform: Pin Grid Array oder Plastic Quad Flat Package mit 132 Pins

- Betriebsspannung (Kernspannung): 5 V

- Erscheinungsdatum: 17. Oktober 1985

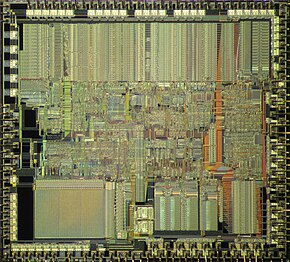

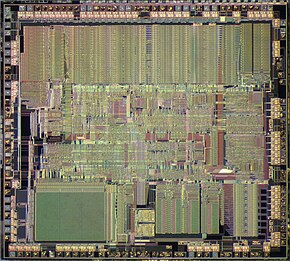

- Fertigungstechnik: Erste Typen CHMOS III mit 1,5 µm, später CHMOS IV mit 1,0 µm

- Die-Größe: 104 mm² (ca. 10 mm × 10 mm, CHMOS III) und 39 mm² (6 mm × 6,5 mm, CHMOS IV)

- Transistoranzahl: 275.000

- Taktraten:

- 12 MHz (erste Modelle des i386)

- 16 MHz

- 20 MHz

- 25 MHz

- 33 MHz

- Prozessoren mit 40 MHz stammten von AMD und von Chips & Technologies.

i386SX

[Bearbeiten | Quelltext bearbeiten]- Prozessor-Cache: Cache befand sich zu diesen Zeiten auf der Hauptplatine, Prozessoren selbst hatten keinen Cache.

- Hauptplatinen-Cache: Üblich waren 64 kB direkt-gemappter Cache bei Prozessoren ab einer Taktrate von 33 MHz.

- Bauform: Plastic Quad Flat Package mit 100 Pins, Pin Grid Array mit 88 Pins

- Betriebsspannung (Kernspannung): 5 V

- Erscheinungsdatum: 16. Juni 1988

- Fertigungstechnik: CHMOS IV, 1,0 µm

- Die-Größe: 104 mm² bei 275.000 Transistoren

- Taktraten:

- 16 MHz

- 20 MHz

- 25 MHz

- 33 MHz

i386SL

[Bearbeiten | Quelltext bearbeiten]

Version des i386SX für tragbare Computer. Mit ihm wurde der System Management Mode (SMM) eingeführt, der zu Stromsparzwecken den Prozessor in Tiefschlaf versetzen kann.

- Prozessor-Cache: Cache befand sich zu diesen Zeiten auf der Hauptplatine, Prozessoren selbst hatten keinen Cache.

- Mainboard-Cache: Üblich waren 16 bis 64 KByte direkt-gemappter Cache.

- Bauform: PGA mit ? Pins, PQFP mit 132 Pins

- Betriebsspannung (Kernspannung): 5 V

- Erscheinungsdatum: 15. Oktober 1990

- Fertigungstechnik: 1,0 µm

- Die-Größe: ? mm² bei 855.000 Transistoren

- Taktraten:

- 20 MHz

- 25 MHz

RapidCAD-1

[Bearbeiten | Quelltext bearbeiten]

- Anzahl der Transistoren: 800.000

- Herstellungsprozess: 0,8 µm

- Cache: on-board, kein on-die-Cache

- Architektur: 80486-Technik mit 80386-Befehlssatz und -Pinout

- Coprozessor: integriert

- Gehäuse: 132 Pin, PGA

- Leistungsaufnahme: 3,5 Watt

- Taktraten: 25 und 33 MHz

RapidCAD-2

[Bearbeiten | Quelltext bearbeiten]

Der RapidCAD-2 ist eine programmierbare logische Anordnung zur Erzeugung des FERR-Signals.

- Eingeführt: 1992

- Anzahl der Transistoren: 275.000

- Herstellungsprozess: 0,8 µm

- Gehäuse: 68 Pin, PGA (für 387er-Sockel)

- Taktraten: 25 und 33 MHz

i376

[Bearbeiten | Quelltext bearbeiten]

Der i376 ist ein Embedded-Prozessor auf Basis des i386SX und kann als Vorgänger des i386EX angesehen werden. Er unterstützt keinen Real Mode und kein Paging.

- Datenbus: 16 Bit

- Adressbus: 24 Bit

- Cache: nicht vorhanden

- Bauform: PQFP mit 100 Pins und PGA-88

- Betriebsspannung (Kernspannung): 5 V

- Erscheinungsdatum: 16. Januar 1989

- Einstellung der Produktion: 15. Juni 2001

- Fertigungstechnik: CHMOS IV, 1,0 µm

- Die-Größe: ?

- unterstützte FPU: 80387SX

- Besonderheiten: bootet im Protected Mode (unterstützt keinen Real-Mode)

- Taktraten: 16 und 20 MHz

i386EX, i386EXTB und i386EXTC

[Bearbeiten | Quelltext bearbeiten]

Embedded-PC-Version des i386SX mit System- und Powermanagement.

- Funktionen

- zwei 82C59A-Interrupt-Controller

- Timer, Counter (drei Kanäle)

- asynchrone SIO (zwei Kanäle)

- synchrone SIO (ein Kanal)

- Watchdog-Timer (Hardware/Software)

- Parallel I/O

- Datenbus: 16 Bit

- Adressbus: 26 Bit

- L1-Cache: nicht vorhanden

- externe FPU: i387SX oder i387SL

- Bauform: PQFP mit 132 Pins, SQFP mit 144 Pins und PGA mit 168 Pins

- Betriebsspannung (Kernspannung): 2,7 bis 5,5 V

- Erscheinungsdatum: 1994

- Fertigungstechnik: 0,8 µm

- Die-Größe: ? mm² bei ? Transistoren

- Taktraten:

- 16 MHz – i386EX, bei 2,7 V bis 3,3 V

- 20 MHz – i386EX, bei 3,0 V bis 3,6 V

- 25 MHz – i386EX, bei 4,5 V bis 5,5 V

- 20 MHz – i386EXTB, bei 2,7 V bis 3,6 V

- 25 MHz – i386EXTB, bei 3,0 V bis 3,6 V

- 25 MHz – i386EXTC, bei 4,5 V bis 5,5 V

- 33 MHz – i386EXTC, bei 4,5 V bis 5,5 V

i386CXSA und i386SXSA (auch als i386SXTA)

[Bearbeiten | Quelltext bearbeiten]

Embedded-PC-Prozessor mit transparentem Power-Management-Modus, integrierter Memory Management Unit und TTL-kompatiblen Eingängen (nur SXSA-Version).

- Datenbus: 16 Bit

- Adressbus: 26 Bit (24 Bit bei i386SXSA)

- CPU-Cache: nicht vorhanden

- externe FPU: i387SX oder i387SL

- Bauform: PQFP mit 100 Pins

- Betriebsspannung (Kernspannung):

- 4,5 V bis 5,5 V (25 und 33 MHz)

- 4,75 V bis 5,25 V (40 MHz)

- Erscheinungsdatum:

- Fertigungstechnik: CHMOS V, 0,8 µm

- Die-Größe: ? mm² bei ? Transistoren

- Taktraten: 25, 33 und 40 MHz

i386CXSB

[Bearbeiten | Quelltext bearbeiten]Embedded-PC-Prozessor mit transparentem Powermanagement-Modus und integrierter Memory Management Unit.

- Datenbus: 16 Bit

- Adressbus: 26 Bit

- CPU-Cache: nicht vorhanden

- externe FPU: i387SX oder i387SL

- Bauform: PQFP mit 100 Pins

- Betriebsspannung (Kernspannung):

- 3,0 V bei 16 MHz

- 3,3 V bei 25 MHz

- Erscheinungsdatum:

- Fertigungstechnik: CHMOS V, 0,8 µm

- Die-Größe: ? mm² bei ? Transistoren

- Taktraten: 16 und 25 MHz

Andere Hersteller

[Bearbeiten | Quelltext bearbeiten]

AMD

IBM

Siehe auch

[Bearbeiten | Quelltext bearbeiten]Weblinks

[Bearbeiten | Quelltext bearbeiten]Einzelnachweise

[Bearbeiten | Quelltext bearbeiten]- ↑ Christof Windeck: 64-Bit-Namen. In: Heise online. 28. April 2008. Abgerufen am 19. November 2016.; Zitat: „Dafür nutzte Intel die Abkürzung IA-32 (Intel Architecture, 32 Bit).“.

- ↑ Stand: Januar 2024

- ↑ https://devblogs.microsoft.com/oldnewthing/20110112-00/?p=11773 My, what strange NOPs you have! by Raymond Chen

- ↑ https://books.google.de/books?id=FeIuiOQN-nEC&lpg=PA1&hl=de&pg=PT330#v=onepage&q&f=false Detecting Step Levels by Jeff Prosise PC Mag 11. Februar 1992 (englisch)

- ↑ Zur damaligen Zeit gab es: 16 und 20 MHz-CPUs auf Mainboards, die RAM-Zugriffe ohne Wartezyklen absolvierten (0 W/S), 25 MHz-CPUs auf Mainboards ohne Cache, die RAM-Zugriffe mit einem Wartezyklus absolvierten (1 W/S) und dadurch kaum schneller als 20 MHz-CPUs waren, sowie CPUs mit 25 und 33 MHz (Intel) oder 40 MHz (AMD) mit üblicherweise 64 KByte Cache, die auf den Cache ohne Wartezyklen zugreifen konnten und dadurch von der höheren Taktfrequenz profitierten. Üblicherweise wurden diese mit 386-25-Cache oder 386-33-Cache beworben.