PCI Express

| PCI Express | |||||

|---|---|---|---|---|---|

| |||||

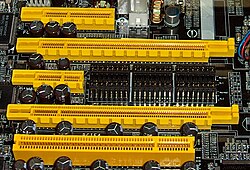

Diferentes ranuras PCIe | |||||

| Información | |||||

| Tipo | conjunto de protocolos | ||||

| Fecha de creación | 2004 | ||||

| Desarrollador | Intel, Dell, HP, IBM | ||||

| Datos técnicos | |||||

| Ancho en bits | 1–32 | ||||

| Velocidad de transferencia |

Para enlaces de línea simple (×1) y de 16-líneas (×16), en cada dirección: | ||||

| Tipo de bus | Serie | ||||

| Interfaz de conexión en caliente | Anteriormente ExpressCard, Mobile PCI Express Module y XQD card | ||||

| Cronología | |||||

| |||||

| pcisig.com | |||||

PCI Express (siendo también oficiales sus abreviaturas PCIe o PCI-e) es un estándar de bus de expansión de tipo serie, designado para sustituir los anteriores estándares PCI, PCO-X y AGP. Actualmente es el estándar más habitual utilizado en placas base para conectar tarjetas gráficas, discos duros, tarjetas de múltiples tipos y, en general, cualquier tipo de componente.

Este sistema fue apoyado principalmente por Intel, que empezó a desarrollar el estándar con nombre de proyecto Arapahoe después de retirarse del sistema Infiniband.

PCI Express es abreviado como PCI-E o PCIe, aunque erróneamente se le suele abreviar como PCI-X o PCIx. Sin embargo, PCI Express no tiene nada que ver con PCI-X OG que es una evolución de PCI, en la que se consigue aumentar el ancho de banda mediante el incremento de la frecuencia, llegando a ser 32 veces más rápido que el PCI 2.1 ya que, aunque su velocidad es mayor que PCI Express, presenta el inconveniente de que al instalar más de un dispositivo la frecuencia base se reduce y pierde velocidad de transmisión.

Estructura

[editar]

Este bus está estructurado como carriles punto a punto, full-duplex, trabajando en serie. En PCIe 1.1 (el más común en 2007) cada carril transporta 250 MB/s en cada dirección. PCIe 2.0 dobla esta tasa a 500 MB/s y PCIe 3.0 la dobla de nuevo (1 GB/s por carril).

Cada ranura de expansión lleva uno, dos, cuatro, ocho o dieciséis carriles de datos entre la placa base y las tarjetas conectadas. El número de carriles se escribe con una x de prefijo (x1 para un carril simple y x16 para una tarjeta con dieciséis carriles); x16 de 500MB/s dan un máximo ancho de banda de 8 GB/s en cada dirección para PCIE 2.x. En el uso más común de x16 para el PCIE 1.1 proporciona un ancho de banda de 4 GB/s (250 MB/s x 16) en cada dirección. En comparación con otros buses, un carril simple es aproximadamente el doble de rápido que el PCI normal; una ranura de cuatro carriles, tiene un ancho de banda comparable a la versión más rápida de PCI-X 1.0, y ocho carriles tienen un ancho de banda comparable a la versión más rápida de AGP.

Una ranura PCi Express 3.0 tiene 1 GB/s direccional y 2 GB/s bidireccional, por lo que logran en el caso de x16 un máximo teórico de 16 GB/s direccionales y 32 GB/s bidireccional

Usos

[editar]

PCI Express está pensado para ser usado solo como bus local, aunque existen extensores capaces de conectar múltiples placas base mediante cables de cobre o incluso fibra óptica. Debido a que se basa en el bus PCI, las tarjetas actuales pueden ser reconvertidas a PCI Express cambiando solamente la capa física. La velocidad superior del PCI Express permitirá reemplazar casi todos los demás buses, AGP y PCI incluidos. La idea de Intel es tener un solo controlador PCI Express comunicándose con todos los dispositivos, en vez de con el actual sistema de puente norte y puente sur.

PCI Express no es todavía suficientemente rápido para ser usado como bus de memoria. Esto es una desventaja que no tiene el sistema similar HyperTransport, que también puede tener este uso. Además no ofrece la flexibilidad del sistema InfiniBand, que tiene rendimiento similar, y además puede ser usado como bus interno externo.

Este conector es usado mayormente para conectar tarjetas gráficas. PCI Express en 2006 es percibido como un estándar de las placas base para PC, especialmente en tarjetas gráficas. Marcas como Advanced Micro Devices y nVIDIA entre otras tienen tarjetas gráficas en PCI Express.

También está siendo utilizado en múltiples ocasiones como puesto para la transferencia de unidades de estado sólido de alto rendimiento, con tasas superiores al Gigabyte por segundo.

Velocidades

[editar]| Versión de PCI Express |

Código en línea | Velocidad de transferencia | Ancho de banda | ||||

|---|---|---|---|---|---|---|---|

| Por carril | En x1 | En x4 | En x8 | En x16 | |||

| 1.0 | 8b/10b | 2,5 GT/s | 2 Gbit/s (250 MB/s) | 250 MB/s (2 Gbit/s) | 1 GB/s (8 Gbit/s) | 2 GB/s (16 Gbit/s) | 4 GB/s (32 Gbit/s) |

| 2.0 | 8b/10b | 5 GT/s | 4 Gbit/s (500 MB/s) | 500 MB/s (4 Gbit/s) | 2 GB/s (16 Gbit/s) | 4 GB/s (32 Gbit/s) | 8 GB/s (64 Gbit/s) |

| 3.0 | 128b/130b | 8 GT/s | 7,9 Gbit/s (984,6 MB/s) | 985 MB/s | 3,9 GB/s | 7,8 GB/s | 15,8 GB/s (126 Gbit/s) |

| 4.0 | 128b/130b | 16 GT/s | 15,8 Gbit/s (1969,2 MB/s) | 1,9 GB/s | 7,8 GB/s | 15,8 GB/s | 31,5 GB/s (252,1 Gbit/s) |

| 5.0 | 128b/130b | 32 GT/s | 31,6 Gbit/s (3938,4 MB/s) | 3,9 GB/s | 15,8 GB/s | 31,5 GB/s | 63 GB/s (504 Gbit/s) |

| 6.0 | 242b/256b | 64 GT/s | 64 Gbit/s (7877 MB/s) | 7,5 GB/s | 30,2 GB/s | 60,5 GB/s | 126 GB/s (1008 Gbit/s) |

pin out

[editar]La siguiente tabla identifica los conductores a cada lado del conector de borde en una tarjeta PCI Express. El lado de soldadura de la placa de circuito impreso (PCB) es el lado A y el lado del componente es el lado B. Los pines PRSNT1# y PRSNT2# deben ser ligeramente más cortos que el resto para garantizar que una tarjeta conectable en caliente esté completamente insertada.

El pin WAKE# utiliza voltaje completo para reactivar la computadora, pero debe estar alto desde la alimentación de espera para indicar que la tarjeta tiene capacidad para reactivarse

| Pin | lado B | Lado A | Descripción | Pin | lado B | Lado A | Descripción | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12 V | PRSNT1# | Debe conectarse al pin PRSNT2# más lejano | 50 | HSOp(8) | Reserved | El carril 8 transmite datos, + y − | |

| 2 | +12 V | +12 V | Pines de alimentación principales | 51 | HSOn(8) | Ground | ||

| 3 | +12 V | +12 V | 52 | Ground | HSIp(8) | El carril 8 recibe datos, + y − | ||

| 4 | Ground | Ground | 53 | Ground | HSIn(8) | |||

| 5 | SMCLK | TCK | Pines de puerto SMBus y JTAG | 54 | HSOp(9) | Ground | El carril 9 transmite datos, + y − | |

| 6 | SMDAT | TDI | 55 | HSOn(9) | Ground | |||

| 7 | Ground | TDO | 56 | Ground | HSIp(9) | El carril 9 recibe datos, + y − | ||

| 8 | +3.3 V | TMS | 57 | Ground | HSIn(9) | |||

| 9 | TRST# | +3.3 V | 58 | HSOp(10) | Ground | El carril 10 transmite datos, + y − | ||

| 10 | +3.3 V aux | +3.3 V | Alimentación auxiliar y Standby power | 59 | HSOn(10) | Ground | ||

| 11 | WAKE# | PERST# | Reactivación de enlaces; reinicio fundamento | 60 | Ground | HSIp(10) | El carril 10 recibe datos, + y − | |

| Muesca | 61 | Ground | HSIn(10) | |||||

| 12 | CLKREQ# | Ground | Señal de solicitud de reloj | 62 | HSOp(11) | Ground | El carril 11 transmite datos, + y − | |

| 13 | Ground | REFCLK+ | Par diferencial de reloj de referencia | 63 | HSOn(11) | Ground | ||

| 14 | HSOp(0) | REFCLK− | El carril 0 transmite datos, + y − | 64 | Ground | HSIp(11) | El carril 11 recibe datos, + y − | |

| 15 | HSOn(0) | Ground | 65 | Ground | HSIn(11) | |||

| 16 | Ground | HSIp(0) | El carril 0 recibe datos, + y − | 66 | HSOp(12) | Ground | El carril 12 transmite datos, + y − | |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | Ground | |||

| 18 | Ground | Ground | 68 | Ground | HSIp(12) | El carril 12 recibe datos, + y − | ||

| PCI Express x1 cards end at pin 18 | 69 | Ground | HSIn(12) | |||||

| 19 | HSOp(1) | Reserved | Lane 1 transmit data, + and − | 70 | HSOp(13) | Ground | El carril 13 transmite datos, + y − | |

| 20 | HSOn(1) | Ground | 71 | HSOn(13) | Ground | |||

| 21 | Ground | HSIp(1) | Lane 1 receive data, + and − | 72 | Ground | HSIp(13) | El carril 13 recibe datos, + y − | |

| 22 | Ground | HSIn(1) | 73 | Ground | HSIn(13) | |||

| 23 | HSOp(2) | Ground | Lane 2 transmit data, + and − | 74 | HSOp(14) | Ground | El carril 14 transmite datos, + y − | |

| 24 | HSOn(2) | Ground | 75 | HSOn(14) | Ground | |||

| 25 | Ground | HSIp(2) | Lane 2 receive data, + and − | 76 | Ground | HSIp(14) | El carril 14 recibe datos, + y − | |

| 26 | Ground | HSIn(2) | 77 | Ground | HSIn(14) | |||

| 27 | HSOp(3) | Ground | Lane 3 transmit data, + and − | 78 | HSOp(15) | Ground | El carril 15 transmite datos, + y − | |

| 28 | HSOn(3) | Ground | 79 | HSOn(15) | Ground | |||

| 29 | Ground | HSIp(3) | Lane 3 receive data, + and −

"Power brake", active-low to reduce device power |

80 | Ground | HSIp(15) | El carril 15 recibe datos, + y − | |

| 30 | PWRBRK# | HSIn(3) | 81 | PRSNT2# | HSIn(15) | |||

| 31 | PRSNT2# | Ground | 82 | Reserved | Ground | |||

| 32 | Ground | Reserved | ||||||

| PCI Express x4 cards end at pin 32 | ||||||||

| 33 | HSOp(4) | Reserved | El carril 4 transmite datos, + y − | |||||

| 34 | HSOn(4) | Ground | ||||||

| 35 | Ground | HSIp(4) | El carril 4 recibe datos, + y − | |||||

| 36 | Ground | HSIn(4) | ||||||

| 37 | HSOp(5) | Ground | El carril 5 transmite datos, + y − | |||||

| 38 | HSOn(5) | Ground | ||||||

| 39 | Ground | HSIp(5) | El carril 5 recibe datos, + y − | |||||

| 40 | Ground | HSIn(5) | ||||||

| 41 | HSOp(6) | Ground | El carril 6 transmite datos, + y − | |||||

| 42 | HSOn(6) | Ground | ||||||

| 43 | Ground | HSIp(6) | El carril 6 recibe datos, + y − | Legend | ||||

| 44 | Ground | HSIn(6) | Ground pin | Referencia de cero voltios | ||||

| 45 | HSOp(7) | Ground | El carril 7 transmite datos, + y − | Power pin | Suministra energía a la tarjeta PCIe. | |||

| 46 | HSOn(7) | Ground | Card-to-host pin | Señal de la tarjeta a la placa base. | ||||

| 47 | Ground | HSIp(7) | El carril 7 recibe datos, + y − | Host-to-card pin | Señal de la placa base a la tarjeta. | |||

| 48 | PRSNT2# | HSIn(7) | Open drain | Puede ser bajado o detectado por varias tarjetas | ||||

| 49 | Ground | Ground | Sense pin | Atados juntos en tarjeta | ||||

| Las tarjetas PCI Express x8 terminan en el pin 49 | Reserved | No utilizado actualmente, no conectar | ||||||

energía sin alimentación externa

[editar]

Todas las tarjetas PCI express pueden consumir hasta 3 A con +3.3 V (9.9 W). La cantidad de +12 V y la potencia total que pueden consumir depende del factor de forma y la función de la tarjeta::: 35–36 [2]

- Las tarjetas x1 están limitadas a 0,5 A a +12 V (6 W) y 10 W combinados.

- Las tarjetas x4 y más anchas están limitadas a 2,1 A a +12 V (25 W) y 25 W combinados.

- La tarjeta de tamaño x1 puede consumir hasta los límites de 25 W después de la inicialización y configuración del software como dispositivo de alta potencia.

- Una tarjeta gráfica x16 de tamaño completo puede consumir hasta 5,5 A a +12 V (66 W) y 75 W combinados después de la inicialización y configuración del software como un dispositivo de alta potencia.: 38–39

Conectores de alimentación de 6 y 8 pines

[editar]

Los conectores opcionales añaden (6 pines) u (8 pines) de alimentación de +12 V para un total de (2 × 75 W + 1 × 150 W).

El pin Sense0 está conectado a tierra mediante el cable o la fuente de alimentación, o flota a bordo si el cable no está conectado.

El pin Sense1 está conectado a tierra mediante el cable o la fuente de alimentación, o flota a bordo si el cable no está conectado.

Algunas tarjetas usan dos 8-

conectores de clavijas, pero esto aún no se ha estandarizado en 2018, por lo que dichas tarjetas no deben llevar el logotipo oficial de PCI Express. Esta configuración permite 375 W en total (1 × 75 W + 2 × 150 W) y probablemente estará estandarizada por PCI-SIG con el estándar PCI Express 4.0.Plantilla:Actualización en línea El 8-

El conector PCI Express de pines podría confundirse con el conector EPS12V, que se utiliza principalmente para alimentar sistemas SMP y multinúcleo. Los conectores de alimentación son variantes de los conectores de la serie Molex Mini-Fit Jr.

| Pins | Hembra/receptáculo

en cable PS |

Macho/ángulo recto

encabezado en PCB |

|---|---|---|

| 6-pin | 45559-0002 | 45558-0003 |

| 8-pin | 45587-0004 | 45586-0005, 45586-0006 |

- ↑ «Where Does PCIe Cable Go?» (en inglés estadounidense). 16 de enero de 2022. Consultado el 10 de junio de 2022.

- ↑ PCI Express Base Specification, Revision 1.1 Page 332

Factores de forma

[editar]- Tarjeta de baja altura

- Mini Card: un reemplazo del formato Mini PCI (con buses PCIe x1, USB 2.0 y SMBus en el conector). Actualmente, el estándar M.2 ha reemplazado en muchos dispositivos al Mini PCI.

- ExpressCard: sucesor del formato PC card (con PCIe x1 y USB 2.0; conectable en caliente)

- XMC: similar al formato CMC/PMC (con PCIe x4 o Serial RapidI/O)

- AdvancedTCA: un complemento de CompactPCI y PXI para aplicaciones tecnológicas; soporta topologías de backplane basadas en comunicación serial

- AMC: un complemento de la especificación AdvancedTCA; soporta procesadores y módulos de entrada/salida en placas ATCA (PCIe x1,x2,x4 o x8).

- PCI Express External Cabling[1]

- Mobile PCI Express Module (MXM) Una especificación de módulos gráficos para portátiles creada por NVIDIA.

- Advanced Express I/O Module (AXIOM) diseño de módulos gráficos creada por ATI Technologies.

Véase también

[editar]Referencias

[editar]- ↑ «PCI Express External Cabling 1.0 Specification». Consultado el 9 de febrero de 2012.

Enlaces externos

[editar] Wikimedia Commons alberga una galería multimedia sobre PCI Express.

Wikimedia Commons alberga una galería multimedia sobre PCI Express.