Programmable Logic Device

In elettronica digitale, un Programmable Logic Device (PLD, lett. "dispositivo a logica programmabile") è un circuito logico digitale realizzato utilizzando tecniche VLSI, caratterizzato dalla capacità di implementare una funzione logica arbitraria impostata successivamente alla fase di produzione e commercializzazione.

I PLD vengono comunemente utilizzati nello sviluppo di circuiti logici ad alte prestazioni come alternativa agli ASIC, più performanti ma decisamente più costosi e tediosi da utilizzare.

Questi dispositivi non sono programmabili nel senso informatico del termine; per distinguerli, si potrebbero chiamare "configurabili", poiché la loro "programmazione" consiste nella scelta di una tra le configurazioni possibili.[1]

Il metodo di configurazione dipende dalla tipologia del dispositivo ed è direttamente correlato al "grado di programmabilità".[2]

Storia

[modifica | modifica wikitesto]Questo tipo di dispositivi sono stati ideati a partire dalla nella seconda metà degli anni 1960, con lo sviluppo presso i laboratori della Harris Semiconductor di una "matrice di diodi configurabile". Nel 1970 la Texas Instrument realizzò il primo circuito integrato basato interamente su ROAM (Read Only Associative Memory) coniando il termine PLA (Programmable Logic Array). Quasi nello stesso periodo, la Harris introdusse nel mercato le PROM (Programmable Read Only Memory) che, oltre che come memorie a sola lettura, trovarono impiego nella realizzazione di semplici macchine a stati o decodificatori di indirizzo. Nel 1973 National Semiconductor produsse una versione semplificata di componenti PLA, denominata DM7575/DM8575, caratterizzata da soli 14 ingressi ed 8 uscite e senza elementi di memoria integrati. Ulteriori progressi furono realizzati nel 1978, con l’introduzione nel mercato dei primi componenti PAL (Programmable Array Logic) ad opera della Monolithic Memories, Inc. che utilizzava il linguaggio di programmazione, denominato PALASM (PALA ASseMbler), simile al FORTRAN, ma con una sintassi semplice e che consentiva di descrivere funzioni logiche complesse.

Caratteristiche

[modifica | modifica wikitesto]I linguaggi di programmazione utilizzati

[modifica | modifica wikitesto]Di solito è difficile e poco conveniente scrivere a mano il codice per programmare i PLD, e quindi si usano computer e software appositi, chiamati logic compiler, simili ai classici compilatori che generano i programmi software eseguibili a partire dai file sorgente. Nel caso dei PLD i linguaggi sorgente si chiamano hardware description language (HDL). Ad esempio il linguaggio ABEL è adatto a logiche di bassa complessità, il Verilog e il VHDL sono indicati per applicazioni più complesse.

La memorizzazione della configurazione

[modifica | modifica wikitesto]Un PLD contiene componenti sia di logica che di memoria, che contiene le informazioni di configurazione. Le memorie possono essere di tipo:

Gli antifusibili al silicio sono usati nelle PAL e sono realizzati applicando una tensione fra due punti dello strato di silicio interno del chip. Hanno questo nome perché funzionano in modo opposto ai fusibili, che inizialmente conducono e si interrompono al passaggio della corrente di guasto.

Le SRAM e le RAM sono memorie volatili, quindi la programmazione viene persa allo spegnimento e deve essere ricaricata alla riaccensione, di solito automaticamente, a cura di una parte dedicata del circuito. Le memorie flash sono non-volatili, cioè mantengono i dati anche a circuito non alimentato e possono essere facilmente cancellate e riprogrammate. Una cella EPROM è basata su transistor di tipo MOS che possono essere messi in stato ON confinando permanentemente cariche elettriche nel terminale gate. La programmazione si effettua usando un apparecchio chiamato PAL programmer. Le cariche rimangono memorizzate per molti anni, e possono essere rimosse esponendo il chip a radiazioni ultraviolette di forte intensità emesse dalla lampada di un cancellatore di EPROM.

Il rapporto con l'utilizzo di ROM

[modifica | modifica wikitesto]Prima dell'introduzione dei PLD si utilizzavano componenti ROM per implementare una qualsiasi logica combinatoria a partire da un dato insieme di ingressi. Una ROM con m ingressi (che corrispondono agli indirizzi) ed n uscite (che corrispondono ai dati) può contenere parole di n bit. Immaginiamo ora che gli ingressi non siano costituiti da un indirizzo di m bit, ma invece da m segnali logici indipendenti. Teoricamente esistono diverse possibili funzioni booleane di questi m segnali, ma la struttura della ROM permette di definire soltanto n di queste funzioni sui terminali di uscita. La ROM, in altre parole, diventa equivalente ad n circuiti logici separati, ciascuno dei quali realizza una data funzione combinatoria degli m ingressi. Il vantaggio di usare una ROM in questo modo consiste nel fatto che ogni possibile funzione degli m ingressi può essere associata a ciascuna delle n uscite, in modo da realizzare un circuito logico combinatorio dotato della massima flessibilità.

Le PROM (ROM programmabili), le EPROM (PROM cancellabili con raggi ultravioletti), e le EEPROM (PROM cancellabili elettricamente) possono essere configurate e programmate mediante apparecchiature facilmente reperibili, senza la necessità di ricorrere a particolari dispositivi hardware o software. In generale si può distinguere tra dispositivi logici programmabili una sola volta o più volte ovvero riprogrammabili. Questi dispositivi, tuttavia, a fronte della loro genericità logica finalizzata alla programmazione specifica, presentano una serie di limitazioni:

- sono solitamente più lenti dei corrispondenti circuiti logici dedicati ovvero specific purpose (ASIC),

- non sono sempre immuni da errori in caso di transizioni asincrone,

- consumano più potenza,

- poiché sono spesso utilizzati solo per una piccola parte della loro capacità teorica, comportano un'eccessiva occupazione di spazio,

- non possono essere facilmente impiegati per implementare circuiti a logica sequenziale poiché non dispongono della funzione flip-flop.

Alcuni dei più semplici modelli di EPROM, come il 2716, sono ancor oggi a volte utilizzati in questo modo, specialmente dai progettisti dilettanti (le "PAL dei poveri", come sono a volte scherzosamente definite).

Tipologie

[modifica | modifica wikitesto]L'interesse per i sistemi riconfigurabili, ossia per quei circuiti che contengono varie funzionalità standard che possono essere modificate dal programma che gira sul processore, tende oggi ad aumentare. La corretta progettazione di questo tipo di dispositivi richiede al progettista un particolare approccio sistemistico e sarà probabilmente accompagnata e facilitata dalla disponibilità di nuovi strumenti software di sviluppo.

Sono già sul mercato PLD che incorporano un microprocessore che esegue le funzioni base (detto core) intorno a cui sono cablate le logiche programmabili. Questa configurazione permette al progettista di concentrarsi sulle funzionalità specifiche da aggiungere, senza preoccuparsi del lavoro che il processore deve svolgere in background.

PLA

[modifica | modifica wikitesto]Si tratta del più semplice dispositivo logico programmabile, ed il primo ad essere stato prodotto a livello industriale verso la fine degli anni '70.

La struttura di una PLA è basata sul fatto che qualsiasi funzione logica può essere descritta tramite somme di prodotti logici. Un PLA è composto da una matrice d'ingresso di porte logiche AND programmabili, collegate con una serie di OR programmabili. L'architettura di un PLA comprende inoltre linee di retroazione dall'uscita all'array di porte AND, che possono essere utilizzate come ingressi aggiuntivi.

I primi dispositivi PLA ad essere stati prodotti implementano circuiti puramente combinatori, successivamente si sono sviluppati PLA sequenziali, che hanno la medesima architettura dei precedenti ma sono dotati di flip-flop per la sincronizzazione dei segnali.

PAL

[modifica | modifica wikitesto]I PAL sono un'evoluzione dei PLA, e differiscono principalmente per l'impossibilità di programmare la serie di porte OR. Questi dispositivi presentano inoltre, a seconda del modello, diverse soluzioni architetturali avanzate in più rispetto al suo predecessore.

GAL

[modifica | modifica wikitesto]

Il Generic Array Logic, solitamente abbreviato in GAL, è un'evoluzione del Programmable Array Logic sviluppata dalla Lattice Semiconductor. Queste logiche hanno le stesse caratteristiche delle PAL, con l'aggiunta di dispositivi di output programmabili detti OLMC.

CPLD

[modifica | modifica wikitesto]

Mentre i GAL sono disponibili soltanto in piccole taglie, contenenti l'equivalente di alcune centinaia di porta logiche, i CPLD consentono di realizzare circuiti logici più complessi. Questi dispositivi contengono l'equivalente di molte PAL collegate fra di loro mediante interconnessioni programmabili ed incapsulate in un unico circuito integrato. Le CPLD possono equivalere a migliaia, a volte addirittura centinaia di migliaia di porte logiche.

Alcuni tipi di CPLD si programmano usando il PAL programmer, ma questo metodo diventa poco pratico quando si devono collegare componenti con centinaia di pin. Un metodo molto più efficiente consiste nel saldare i dispositivi su un circuito stampato e quindi inviare loro, mediante un PC, un flusso di dati che, opportunamente decodificati dai circuiti interni dei CPLD, conferiscono agli stessi la configurazione necessaria a realizzare le funzioni logiche desiderate.

Ciascun produttore ha un proprio nome che identifica questa modalità di programmazione. Per esempio, la Lattice Semiconductor lo chiama "in-system programming". È in corso al riguardo un progetto di standardizzazione da parte del JTAG (Joint Test action Group).

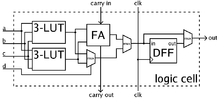

FPGA

[modifica | modifica wikitesto]

Mentre le PAL si stavano evolvendo nelle GAL e nei CPLD, una nuova famiglia di dispositivi, basata sulla tecnologia gate-array si stava affermando con il nome di FPGA. Un esempio è il modello 82s100 prodotto dalla Signetics verso la fine degli anni 1970. Tali dispositivi utilizzano una matrice di porte logiche molto simile a quella di un normale gate array, ma la programmazione è fatta dall'utilizzatore anziché in fabbrica.

La definizione di "field programmable" (cioè "programmabile sul campo") può sembrare poco chiara, ma il termine "field" significa semplicemente sul campo "fuori dalla fabbrica", quindi nel luogo dove viene utilizzato dall'utente finale. Le FPGA, come i CPLD, si programmano dopo averle saldate al circuito stampato. La loro configurazione è volatile e deve essere ricaricata ad ogni riaccensione ed ogni volta che si richiede una diversa programmazione.

FPGA e CPLD sono di solito soluzioni equivalenti dal punto di vista delle prestazioni. La scelta può dipendere da considerazioni economiche o dall'esperienza personale del progettista.

Note

[modifica | modifica wikitesto]- ^ Napoli 2023, cap. 7.5.

- ^ Napoli 2023, cap. 4.2.2.

Bibliografia

[modifica | modifica wikitesto]- Ettore Napoli, Progetto di circuiti digitali e implementazione su FPGA, Bologna, Società Editrice Esculapio, 2023, ISBN 978-88-9385-350-7.

Voci correlate

[modifica | modifica wikitesto]- Complex Programmable Logic Device

- Field programmable gate array

- Generic Array Logic

- Programmable Logic Array

- Simple Programmable Logic Device

Altri progetti

[modifica | modifica wikitesto] Wikimedia Commons contiene immagini o altri file sul Programmable Logic Device

Wikimedia Commons contiene immagini o altri file sul Programmable Logic Device