UltraSPARC T1

| UltraSPARC T1 Microprocesor | |

| Informație generală | |

|---|---|

| Lansat | 2005 |

| Proiectat de | Sun Microsystems |

| Fabricanți principali | Texas Instruments |

| Set de instrucțiuni | SPARC V9 |

| Performanța | |

| Frecvența de ceas maximă a UCP | 1.0 GHz până la 1.4 GHz |

| Arhitectura și clasificarea | |

| Specificații fizice | |

| Nuclee | 4, 6, 8 |

| Modifică date / text | |

Microprocesorul UltraSPARC T1 de la Sun Microsystems cunoscut sub numele de cod „Niagara” este un procesor multinucleu și multithread proiectat special pentru aplicațiile server care rulează pe mai multe fire de execuție. Dezvoltat special pentru a reduce consumul de energie reușește să consume 63W la o frecvență de ceas de 1,2 GHz și o tensiune de alimentare de 1,2V.

T1 a fost creat ca un procesor multinucleu, putând avea maxim 8 nuclee și câte 4 fire de execuție pe fiecare nucleu. Această arhitectură este potrivită pentru aplicații de tip baze de date și servicii web care au un număr ridicat de fire de execuție. Procesorul suportă partiționarea nucleelor astfel încat un grup de nuclee să ruleze un set de procese/fire de execuție și celelalte nuclee să se ocupe de restul sistemului.

UltraSPARC T1 este alcătuit din 279 milioane de tranzistoare pe o arie de 378 mm² și este fabricat de Texas Instruments folosind tehnologia lor CMOS de 90 nm.[1]

Arhitectură

[modificare | modificare sursă]Microprocesorul UltraSPARC T1 a fost dezvoltat de la zero ca un procesor multinucleu și multithread rulând un număr maxim de 32 de fire de execuție. Nucleele au fost proiectate să fie cât mai simple pentru a rula cât mai multe fire de execuție și a utiliza eficient pipeline-ul. Numărul mare de fire de execuție permite îmbunătățirea performanțelor sistemului prin comutarea firelor de execuție atunci când apar rateuri de cache și întârzierea datorată accesului la memoriei principală este mare.

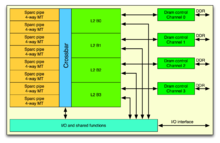

Fiecare nucleu are disponibilă o cantitate de 16ko de memorie cache de nivel 1 pentru instrucțiuni și 8ko de memorie cache de nivel 1 pentru date. Cele 8 nuclee ale unui T1 au acces la o memorie comună cache de nivel 2 printr-o rețea de interconectare de tip crossbar. Cache-ul de nivel 2 are o dimensiune de 3Mo și este împărțit în 4 bancuri pentru a asigura lățimea de bandă necesară deservirii celor 8 nuclee. Fiecare banc de memorie cache de nivel 2 este conectat la un singur controler de memorie DRAM care face legatura cu memorii de tip DDR2-SDRAM. În plus toate bancurile sunt conectate la interfețele de comunicație J-BUS si SSI.

Interfața J-BUS interconectează procesorul UltraSPARC cu subsistemul de intrare/ieșire. Este o magistrala de 128 biți, 200 Mhz, cu adresele și datele multiplexate folosită predominant pentru trafic cu acces direct la memorie și trafic PIO pentru control. Interfața serială (SSI) are o rată de 50 Mo/s și conectează procesorul la un ASIC extern care face legatura cu o memorie ROM folosită la bootare.

Rețeaua de interconectare crossbar realizează interconexiuni dinamice în funcție de necesități între cele 8 nuclee, memoria cache de nivel 2, unitatea de virgulă mobilă și unitatea IOB.

Dezavantaje

[modificare | modificare sursă]Prezența unei singure unități de virgulă mobilă face ca procesorul să fie nerecomandat pentru aplicații în care predomanină astfel de calcule. Un alt dezavantaj îl reprezintă imposibilitatea folosirii într-un sistem multiprocesor.

Majoritatea acestor dezavantaje au fost deja corectate în UltraSPARC T2 și generațiile următoare.

Arhitectură deschisă

[modificare | modificare sursă]Când au început livrarea microprocesorului T1, Sun a anunțat că va face publică arhitectura acestuia sub Licența Publică Generală GNU și pe data de 21.03.2006 a fost creat proiectul OpenSPARC. Informațiile care au fost publicate includ:

- Sursele Verilog pentru UltraSPARC T1;

- O suită de modele folosite pentru verificare și simulare;

- Documente continând descrierea arhitecturii și a setului de instructiuni;

- Imaginile necesare pentru simularea sistemului de operare Solaris 10;

- Codul sursă a nivelului software Hypervisor;

Bibliografie

[modificare | modificare sursă]en P. Kongetira, K. Aingaran, K. Olukotun, Niagara: A 32-Way Multithreaded SPARC Processor, IEEE computer Society, 2005

en James Laudon, UltraSPARC T1: A 32-threaded CMP for Servers Arhivat în , la Wayback Machine., Sun Microsystems

en David L. Weaver, OpenSPARC™ Internals, Sun Mycrosystems, Santa Clara, 2008 ISBN 978-0-557-01974-8

en OpenSPARC™ T1 Microarchitecture Specification, Sun Microsystems, 2006

Note

[modificare | modificare sursă]- ^ McGhan, Harlan (6.11.2006). "Niagara 2 Opens the Floodgates", p.5