IBM 7030

IBM 7030, також відомий як Stretch — перший суперкомп'ютер компанії IBM, побудований на транзисторах. Був найшвидшою ЕОМ у світі з 1961 до 1964 року, коли запрацювала перша машина CDC 6600.[1][2]

Машину було спроектовано під потреби, сформульовані Едвардом Теллером з Ліверморської національної лабораторії; перший екземпляр було поставлено Лос-Аламоській національній лабораторії у 1961-му, а другий — у вигляді зміненої версії, що отримала назву IBM 7950 Harvest — Агентству національної безпеки у 1962-му. У атомному центрі Алдермастон (Велика Британія) комп'ютер інтенсивно використовувався для досліджень, після того, як було розроблено компілятор з Фортрана «S2» з підтримкою динамічних масивів.[3][4]

Збудовані IBM 7030 вийшли значно повільнішими, ніж очікувалося, і так і не змогли досягнути запланованих показників швидкодії (досить агресивних для часу). Компанія IBM була змушена знизити ціну з 13,5 мільйонів доларів США до 7,78 мільйонів, і припинити продаж машини (крім замовників, що вже підписали контракти). Журнал PC World назвав IBM Stretch однією з найбільших невдач проект-менеджменту в історії інформаційних технологій.[5]

Всередині самої IBM той факт, що їх випередила невелика Control Data Corporation, сприймався досить важко.[6] Керівника проєкту Стівена Данвелла (Stephen W. Dunwell),[7] було спочатку звинувачено у «провалі»,[8] але коли стало зрозуміло, що успіх наступника Stretch — лінійки System/360 — є безумовним — реабілітовано (керівництво IBM офіційно вибачилось перед Данвеллом, і навіть надало йому титул IBM Fellow у 1966-му році).[9]

Незважаючи на недостатню швидкодію, багато ідей і технологій Stretch знайшли подальший розвиток у лінійці машин IBM System/360, що дебютувала 1964-го року.

На початку 1955 року доктор Едвард Теллер з Радіаційної Лабораторії Каліфорнійського Університету розпочав пошук системи для наукових обчислень в галузі гідродинаміки. Теллер звернувся до IBM та UNIVAC; система мала називатись Livermore Automatic Reaction Calculator, або LARC. Катберт Герд (Cuthbert Hurd), виконавчий директор у IBM, оцінив вартість такої системи приблизно у 2,5 мільйонів доларів, а продуктивність — 1..2 MIPS.[10] Систему мало бути здано до експлуатації через «два-три роки» після підписання контракту.

На заводі IBM у Поукіпзі невелика команда, до якої входили Джон Ґріффіт і Джин Амдаль, почала роботу над дизайном. У момент коли вони закінчили і були готові представити проект, інженер Ральф Палмер зупинив їх зі словами «це помилка».[10] Запропонований дизайн мав бути реалізований або на точкових, або на поверхнево-бар'єрних транзисторах — обидва ці типи, як на той час вже стало відомо, поступалися у швидкодії щойно винайденим дифузійним транзисторам.[10]

IBM проінформувала Ліверморську лабораторію, що розриває контракт, але натомість запропонувала кардинально кращу систему: «Ми не будуватимемо ту машину для вас, ми хочемо збудувати щось набагато краще! Ми не знаємо точно, скільки зусиль і коштів це потребуватиме, але оцінюємо, що ще приблизно один мільйон доларів і один рік. Ми не знаємо точно, наскільки швидко вона працюватиме — десь 10 мільйонів інструкцій за секунду»."[10] Втім, ці цифри не вразили Лівермор, і у травні 1955-го лабораторія оголосила, що UNIVAC виграв контракт на LARC, і що нове ім'я проекту — Livermore Automatic Research Computer. LARC було поставлено і здано до експлуатації у червні 1960-го року.[11]

У вересні 1955-го, на хвилі побоювань, що Лос-Аламоська національна лабораторія також замовить LARC, IBM презентувала чорновий варіант швидкодіючого двійкового комп'ютера на основі дизайну, який відхилили у Ліверморі. У Лос-Аламосі зацікавились, і у січні 1956-го проект Stretch було формально розпочато. У листопаді 1956-го IBM підписав контракт, з досить амбітними цілями щодо продуктивності системи на рівні «принаймні у 100 разів вищому, ніж у IBM 704» (тобто 4 MIPS). Здача проекта замовникові планувалася у 1960 році.

Під час проектування і початкових випробувань стало зрозуміло, що тактову частоту процесора доведеться знизити, і що найімовірніше Stretch не досягне поставлених цілей зі швидкодії. Втім, продуктивність мала вийти як мінімум на рівні 60-кратної IBM 704. У 1960-му було встановлено ціну, 13,5 мільйона доларів. У 1961-му запуск програми тесту продуктивності показав, що реальна швидкодія буде лише на рівні 30-кратної IBM 704 (тобто 1,2 MIPS). Це викликало розгублення і збентеження у IBM, і, як наслідок, у травні 1961-го Уотсон анонсував зниження ціни на всі замовлені IBM 7030 (до 7,8 мільйона доларів), і припинення продажу машини новим замовникам.

Додавання операндів з рухомою комою у IBM 7030 здійснювалося за 1,38..1,5 мікросекунд, множення — 2,48..2,70 мікросекунд, ділення — за 9..9,9 мікросекунд.

Незважаючи на загальне сприйняття IBM 7030 як невдалої системи, багато технологічних рішень і ідей з цієї машини знайшли своє застосування в успішних комп'ютерах майбутнього. Транзисторні логічні схеми, побудовані зі стандартних блоків (Стандартна Модульна Система, SMS) стали основою лінійки машин IBM 7090 (наукові комп'ютери), IBM 7070 і 7080 (бізнес-комп'ютери), сімейств IBM 7040 і IBM 1400, а також невеликого наукового комп'ютера IBM 1620. Феритова пам'ять моделі 7302 Model I застосовувалася також у IBM 7090, IBM 7070 and IBM 7080. Багатозадачність, захист пам'яті, узагальнена схема переривань, восьмибітний байт для вводу-виводу[a] — всі ці інновації знайшли подальший розвиток у лінійці IBM System/360.

Стівен Данвелл, менеджер проекту, якого зробили «цапом-відбувайлом» за невдачі IBM 7030 на ринку, невдовзі після феноменально успішного початку продаж серії System/360 у 1964-му році відзначив, що більшість ключових компонентів серії було випробувано у машині Stretch.[12] 1966-го перед ним вибачились і надали титул IBM Fellow — висока відзнака, що дозволяє вести дослідження на власний вибір використовуючи ресурси компанії.[12]

Конвеєр команд, попередня вибірка і декодування інструкції, паралельні банки пам'яті — ці інновації знайшли своє застосування в пізніших проектах суперкомп'ютерів, таких як IBM System/360 моделі 91 і 95, IBM System/370 моделі 195, і серії IBM 3090, а також у комп'ютерах інших виробників. У більшості сучасних мікропроцесорів ці технології також активно використовуються.

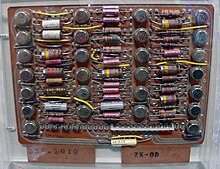

Процесор IBM 7030 побудований на основі схем емітерно-зв'язаної логіки.[13] Всього було 18 типів «стандартних модульних плат» (SMS, Standard Modular System): 4025 двосторонніх (на ілюстрації) і 18747 односторонніх, на яких розміщувалося 169100 транзисторів. Машина споживала 21 кВт від мережі.[14] Транзистори — германієві, дрейфові, підвищеної швидкодії (з робочою частотою до 100 МГц), як n-p-n, так і p-n-p структури, кожен споживав потужність приблизно 50 мВт.[14] У деяких схемах використовувався «третій рівень напруги». Мінімальна затримка проходження логічного сигналу була на рівні 20 нс. У частинах схеми, що вимагали особливо високої швидкодії, застосовувалась логіка на емітерних повторювачах (це дозволяло знизити затримку ще на 10 нс).[14]:55

Тип феритової пам'яті — аналогічний машині IBM 7090.[14]:58

- Лос-Аламоська національна лабораторія, поставка: квітень 1961, початок роботи: травень 1961, зупинка системи: 21 червня 1971.

- Агентство національної безпеки Сполучених Штатів: з лютого 1962 року (процесор системи IBM 7950 Harvest) по 1976 рік (система автоматичної подачі картриджів магнітної стрічки IBM 7955 почала давати збої через зношеність компонентів, тому всю систему HARVEST було вирішено списати).

- Ліверморська національна лабораторія.

- Центр Атомної Зброї Алдермастон, Англія.

- Бюро погоди Сполучених Штатів.

- Корпорація MITRE: машина експлуатувалася до серпня 1971-го; навесні 1972-го продана університету Брігама Янга, де використовувалася у департаменті фізики аж до зупинки і розбирання у 1982-му.

- Військово-морські сили США, центр у Далґрені, Вірджинія.

- IBM.

- Комісаріат атомної енергетики Франції.

IBM 7030 з лабораторії Лоуренса Лівермора (окрім феритової пам'яті) і частини машини, що працювала у MITRE Corporation / Університеті Брігама Янга, зараз знаходяться у колекції Музею комп'ютерної історії у Маунтін-В'ю, Каліфорнія.

- Числа з рухомою комою — змінної ширини, зберігаються або у двійковій (від 1 до 64 біт), або у десятковій (від 1 до 16 цифр) формі, без знаку або зі знаком. При використанні десяткової форми цифри — змінної розрядності (від 4 до 8 біт).

- Числа з рухомою комою мають 1 біт «прапорця експоненти», 10 біт власне експоненти, 1 біт знаку експоненти, 48 біт величини, і 4-бітний знак (у форматі знак/величина).

- Алфавітно-цифрові символи — змінної розрядності (8 біт або менше).

- Змінна ширина байта (від 1 до 8 біт).[15]

Ширина інструкції — 32 або 64 біти.

Регістри відображаються на перші 32 адреси пам'яті.[16]

| Адреса | Мнемоніка | Регістр | Розташування |

|---|---|---|---|

| 0 | $Z | 64-розрядний нуль: тільки для читання (завжди читається нуль) | Головна пам'ять |

| 1 | $IT | інтервальний таймер (розряди 0..18): значення зменшується з частотою 1024 Гц, переповнення кожні 8,5 хвилини, при нульовому значенні виставляє «time signal indicator» у індикаторному регістрі | Індексна пам'ять |

| $TC | 36-розрядний таймер (розряди 28..63): підраховує кількість циклів по 1024 Гц, біти 38..63 збільшуються раз на секунду, переповнення приблизно за 777 діб. | ||

| 2 | $IA | 18-розрядна адреса переривання | Головна пам'ять |

| 3 | $UB | 18-розрядна адреса верхньої границі (upper boundary address, біти 0-17) | Транзисторний регістр |

| $LB | 18-розрядна адреса нижньої границі (lower boundary address, біти 32-49) | ||

| 1-розрядний контроль границі (біт 57): визначає захищеність/незахищеність адреси в межах границі | |||

| 4 | 64-розрядний службовий регістр | Головна пам'ять | |

| 5 | $CA | адреса каналу (розряди 12..18): тільки для читання, встановлюється процесором вводу-виводу | Транзисторний регістр |

| 6 | $CPUS | біти інших процесорів (0..18): механізм повідомлень для кластера до 20 ЦП | Транзисторний регістр |

| 7 | $LZC | лічильник лівих нульових розрядів (біти 17..23): кількість початкових нульових біт результату операції | Транзисторний регістр |

| $AOC | лічильник одиничних розрядів (біти 44..50): кількість одиничних біт результату операції | ||

| 8 | $L | Ліва половина 128-розрядного акумулятора | Транзисторний регістр |

| 9 | $R | Права половина 128-розрядного акумулятора | |

| 10 | $SB | байт знаку акумулятора (біти 0..7) | |

| 11 | $IND | регістр індикатора (біти 0..19) | Транзисторний регістр |

| 12 | $MASK | 64-розрядний регістр маскиr: біти 0..19 завжди 1, біти 20..47 з можливістю запису, біти 48..63 завжди 0 | Транзисторний регістр |

| 13 | $RM | 64-розрядний регістр залишку: встановлюється інструкціями ділення (цілого і з рухомою комою) | Головна пам'ять |

| 14 | $FT | 64-розрядний регістр дільника (може бути змінений лише інструкцією «load factor») | Головна пам'ять |

| 15 | $TR | 64-розрядний транзитний регістр | Головна пам'ять |

| 16 … 31 |

$X0 … $X15 |

64-розрядні індексні регістри (всього 16) | Індексна пам'ять |

Об'єм феритової пам'яті — від 16K to 256K 64-розрядних слів, банками по 16K.

Модулі пам'яті було занурено в мастило, для стабілізації операційних характеристик і уникнення перепаду температур.

- STRETCH Assembly Program (STRAP)

- MCP (не плутати з системою з такою самою назвою для машин Burroughs — Burroughs MCP)

- Мови програмування COLASL і IVY[17]

- Фортран[18]

- IBM 608, перший обчислювальний пристрій на транзисторах (калькулятор з можливістю перекомутації схем), доступний на ринку

- ↑ Хоча у Stretch інструкції могли працювати з байтами довільної ширини, жоден наступний процесор від IBM таку схему не реалізовував. Однак, деякі машини від Burroughs, Control Data Corporation, DEC, General Electric, RCA, UNIVAC та інші мали підтримку байта змінної ширини — аж до ширини машинного слова

- ↑ «CDC 6600, спроектована Сеймуром Креєм, була майже втричі швидша за IBM 7030.» Making a World of Difference: Engineering Ideas into Reality. National Academy of Engineering. 2014. ISBN 0309312655.

- ↑ «У 1964 році CDC 6600 Крея витіснила Stretch з вершини найшвидших ЕОМ світу.» Andreas Sofroniou (2013). EXPERT SYSTEMS, KNOWLEDGE ENGINEERING FOR HUMAN REPLICATION. ISBN 1291595090.

- ↑ Some Early UK FORTRAN Compilers. Архів оригіналу за 27 червня 2017. Процитовано 26 грудня 2017.

- ↑ HARTRAN Overview. Архів оригіналу за 15 жовтня 2017. Процитовано 26 грудня 2017.

- ↑ Widman, Jake (9 жовтня 2008). Lessons Learned: IT's Biggest Project Failures. PCWorld. Архів оригіналу за 5 листопада 2012. Процитовано 23 жовтня 2012.

- ↑ Відома цитата президента Т. Дж. Уотсона молодшого, де він запитує «Чому нас обійшла фірма, де працює 34 людини з прибиральником включно?»Watson Jr. memo about CDC 6600. 28 серпня 1963. Архів оригіналу за 3 січня 2018. Процитовано 26 грудня 2017.

- ↑ IBM Archives: Stephen W. Dunwell. IBM. Архів оригіналу за 15 травня 2017. Процитовано 26 грудня 2017.

- ↑ «Stretch was considered a commercial failure, and Dunwell was sent into …» Smotherman, Mark; Spicer, Dag. IBM's Single-Processor Supercomputer Efforts.

- ↑ « to pursue any research he wished.» Wolfgang Saxon (24 березня 1994). S. W. Dunwell, 80, Engineer at I.B.M.; Designed Computers. The New York Times. Архів оригіналу за 15 жовтня 2017. Процитовано 26 грудня 2017.

- ↑ а б в г Bob Evans (Summer 1984). IBM System/360. The Computer Museum Report. с. 8—18.

- ↑ Charles Cole. The Remington Rand Univac LARC. Архів оригіналу за 26 жовтня 2018. Процитовано 26 грудня 2017.

- ↑ а б Simmons, William W.; Elsberry, Richard B. (1988), Inside IBM: the Watson years (a personal memoir), Pennsylvania, USA: Dorrance, с. 160, ISBN 978-0805931167, архів оригіналу за 18 червня 2013, процитовано 26 грудня 2017. The memoir of a senior IBM executive, giving his recollections of his and IBM's experience from World War II into the 1970s.

{{citation}}: Обслуговування CS1: Сторінки зі значенням параметра postscript, що збігається зі стандартним значенням в обраному режимі (посилання). - ↑ Rymaszewski, E. J. та ін. (1981). Semiconductor Logic Technology in IBM. IBM Journal of Research and Development. 25 (5): 607—608. doi:10.1147/rd.255.0603. ISSN 0018-8646. Архів оригіналу за 11 липня 2017. Процитовано 9 листопада 2017.

- ↑ а б в г Erich Bloch (1959). The Engineering Design of the Stretch Computer (PDF). Eastern Joint Computer Conference. Архів оригіналу (PDF) за 26 вересня 2019. Процитовано 17 травня 2019.

- ↑ Mark Smotherman (July 2010). IBM Stretch (7030) — Aggressive Uniprocessor Parallelism. clemson.edu. Архів оригіналу за 2 жовтня 2017. Процитовано 7 грудня 2013.

- ↑ IBM 7030 Data Processing System Reference Manual (PDF). bitsavers.org. IBM. 1961. с. 34..38. Архів оригіналу (PDF) за 29 вересня 2018. Процитовано 5 травня 2015.

- ↑ Roger B. Lazarus (1978). Computing at LASL in the 1940s and 1950s. Департамент енергетики США. Архів оригіналу за 27 грудня 2017. Процитовано 26 грудня 2017.

- ↑ The IBM 7030 FORTRAN System (PDF). Computer History Museum. IBM Stretch Collection: International Business Machines Corporation. 1961. с. 36. Архів оригіналу (PDF) за 2 квітня 2015. Процитовано 28 лютого 2015.

- Усне інтерв'ю з Джином Амдалем Інститут Чарльза Беббіджа, Університет Міннесоти, Міннеаполіс. Джин Амдаль розповідає про свою роль у проектуванні різних машин IBM, зокрема 7030 (STRETCH), IBM 701, 701A, і IBM 704.

- IBM Stretch Collections @ Computer History Museum [Архівовано 6 січня 2018 у Wayback Machine.]

- Collection index page

- The IBM 7030 FORTRAN System [Архівовано 2 квітня 2015 у Wayback Machine.]

- Collection index page

- 7030 Data Processing System [Архівовано 4 серпня 2004 у Wayback Machine.] (IBM Archives)

- IBM Stretch (aka IBM 7030 Data Processing System) [Архівовано 9 січня 2018 у Wayback Machine.]

- Organization Sketch of IBM Stretch [Архівовано 2 жовтня 2017 у Wayback Machine.]

- BRL report on the IBM Stretch [Архівовано 3 січня 2018 у Wayback Machine.]

- Planning a Computer System — Project Stretch, 1962 book.

- Документація IBM 7030 (у форматі PDF) на сайті Bitsavers.org [Архівовано 18 лютого 2018 у Wayback Machine.]