ADC

Mạch chuyển đổi tương tự ra số hay ADC (viết tắt tiếng Anh: Analog-to-Digital Converter) là hệ thống mạch thực hiện chuyển đổi một tín hiệu analog (tín hiệu tương tự) liên tục, ví dụ như tín hiệu âm thanh thanh micro, hay tín hiệu ánh sáng trong máy ảnh kỹ thuật số, thành tín hiệu số.[1][2] Một hệ thống ADC có thể bao gồm một bộ phận phần cứng (như một bộ tính toán độc lập) làm nhiệm vụ chuyển đổi tín hiệu analog (dưới dạng điện áp hay dòng điện) thành các giá trị số (digital) đại diện cho cường độ điện áp hay tín hiệu đó. Thông thường, tín hiệu số ngõ ra (digital output) mang dạng nhị phân bù 2 (two's complement binary number) tỉ lệ với giá trị ngõ vào, nhưng cũng có một số khả năng khác.

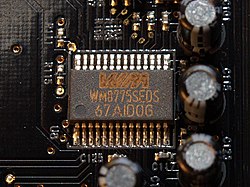

Có một số kiến trúc ADC đang được sử dụng. Do sự phức tạp của kiến trúc và yêu cầu về độ chính xác, phần lớn các hệ thống ADC đều được sản xuất bên trong mạch tích hợp (IC). Tại ngõ vào chính của ADC trong chip có thể có phần tử Multiplexer, cho ra ADC đa ngõ vào hay ADC đa kênh. Trước đây giá thành ADC cao, nên đã bố trí 8 đến 64 ngõ vào. Hiện nay xuất hiện các chip chỉ bố trí 1, 2 hoặc 4 ngõ vào.

Mạch DAC (viết tắt tiếng Anh: Digital-to-Analog Converter) hay Mạch chuyển đổi số ra tương tự có tính năng ngược với mạch ADC khi thực hiện chuyển đổi tín hiệu số sang tín hiệu tương tự.

Hoạt động

[sửa | sửa mã nguồn]Để thực hiện việc chuyển đổi một tín hiệu analog thực tế (như nhiệt độ, độ ẩm, âm thanh,...) thành tín hiệu số, thì tín hiệu analog thực tế này phải được chuyển đổi thành dạng điện áp. Bộ ADC sau đó sẽ đọc các giá trị điện áp này và chuyển đổi thành tín hiệu số tương ứng.[2]

Do quá trình chuyển đổi này liên quan đến việc lượng tử hóa tín hiệu ngõ vào, do đó nhất thiết mắc một lượng lỗi hoặc bị ảnh hưởng bởi nhiễu tín hiệu. Thay vì liên tục thực hiện việc chuyển đổi, bộ ADC thực hiện việc chuyển đổi theo chu kì, lấy mẫu (sampling) tín hiệu ngõ vào, giới hạn băng thông cho phép của tín hiệu.[3]

Hoạt động của một bộ ADC được đặc trưng bởi băng thông và tỉ số tín hiệu trên nhiễu (SNR signal-to-noise ratio). Băng thông của ADC được đặc trưng bởi tốc độ lấy mẫu (sampling rate). Tỉ số SNR của bộ ADC bị ảnh hưởng bởi nhiều yếu tố bao gồm: độ phân giải (resolution), độ tuyến tính (linearity) và độ chính xác (accuracy) (đánh giá tính hiệu quả của quá trình lượng tử hoá tín hiệu từ tính hiệu analog thực tế), aliasing và jitter. Tỉ số SNR của bộ ADC thể hiện số bit trung bình trả về trong mỗi tính toán mà không bị nhiễu, được gọi là số bit hiệu quả (ENOB effective number of bits). Một bộ ADC lý tưởng có số ENOB bằng với độ phân giải của nó.[4]

Độ phân giải

[sửa | sửa mã nguồn]Bậc số hóa là số bit xác định số mức số hóa cho dải giá trị điện áp danh định. Hệ M bit có 2M mức cho tín hiệu đơn cực, chỉ dương hoặc chỉ âm. Nếu là tín hiệu song cực, phải dành 1 bit dấu, và do mức 0 bị dính nên hệ cho ra 2M-1-1 mức.

Dải giá trị điện áp danh định này được gọi là dải động. Điện áp lớn hơn thì gây tràn (overflow).

Alias

[sửa | sửa mã nguồn]Điểm chú ý là tác động của hiện tượng Aliasing đến đặc trưng số hóa, và nó dẫn đến đòi hỏi tần số số hóa phải lớn hơn trên gấp đôi tần cực đại của băng tần tín hiệu trong các nhu cầu thông thường, còn trong nhu cầu kỹ thuật thì là gấp 4, ví dụ phải dùng 1 KHz để số hóa tín hiệu có băng tần 10–250 Hz.

Tốc độ lấy mẫu

[sửa | sửa mã nguồn]Vì tín hiệu analog là liên tục theo thời gian nên cần thiết để chuyển đổi tín hiệu này thành một dãy các giá trị kỹ thuật số. Do đó cần định nghĩa một đại lượng tốc độ đặc trưng cho thời gian mà các giá trị kỹ thuật số (digital values) được lấy mẫu từ tín hiệu analog. Tốc độ này được gọi là tốc độ lấy mẫu hay tần số lấy mẫu. Một tín hiệu analog liên tục có thể được lấy mẫu và sau đó được khôi phục lại dạng tín hiệu gốc ban đầu từ các giá trị mẫu rời rạc theo thời gian bởi bộ lọc khôi phục (reconstruction filter).[5] Định lý lấy mẫu Nyquist–Shannon chỉ ra rằng tín hiệu gốc chỉ có thể được khôi phục lại như ban đầu nếu tốc độ lấy mẫu lớn hơn hoặc bằng 2 lần tần số lớn nhất của tín hiệu gốc.

Do bộ ADC không thể thực hiện việc chuyển đổi tín hiệu tức thời, giá trị đầu vào phải được lưu như hằng số trong thời điểm thực hiện tính toán-chuyển đổi (gọi là thời gian chuyển đổi, conversion time). Khối mạch lấy giá trị lấy mẫu và thực hiện quá trình tính toán-chuyển đổi này trong phần lớn các trường hợp dùng tụ điện để lưu các giá trị analog điện áp đầu vào và sử dụng mạch switch hoặc gate để ngắt kết nối tụ với ngõ vào. Nhiều IC ADC ngày nay đều có thành phần là các khối xử lý đó.

Phân loại

[sửa | sửa mã nguồn]

Flash ADC

[sửa | sửa mã nguồn]Flash ADC là dạng đơn giản nhất, thực hiện bằng dãy điện trở phân áp và các comparator điện áp. Nó là minh hoạ nhập đề cho hoạt động của ADC. Trong hình vẽ là ADC 16 mức "không âm", thực hiện bẳng 15 comparator. Kết quả so được mạch lập mã Encoder tiếp nhận và chuyển sang mã nhị phân, trong trường hợp này là 4 bit.

- Nhịp lấy mẫu do phần nhận mã tự quyết định, và có thể đạt rất cao.

- Thay cho Bậc số hóa phải dùng mức số hoá (nếu số mức không trùng vào số 2M).

ADC xấp xỉ nối tiếp

[sửa | sửa mã nguồn]ADC xấp xỉ nối tiếp (successive-approximation)

Ramp-compare ADC

[sửa | sửa mã nguồn]Ramp-compare ADC

ADC tích phân sườn đôi hoặc đa sườn

[sửa | sửa mã nguồn]Tích phân sườn đôi hoặc đa sườn (dual-slope, multi-slope) ADC

ADC mã hoá delta

[sửa | sửa mã nguồn]ADC Mã hoá delta (delta-encoded ADC or counter-ramp)

ADC sigma-delta

[sửa | sửa mã nguồn]ADC sigma-delta

Các đặc trưng hoạt động

[sửa | sửa mã nguồn]ADC dấu phẩy tĩnh

[sửa | sửa mã nguồn]Các ADC thông thường nêu ở mục trên thực hiện số hóa với các mức tín hiệu cách đều, và cho ra kết quả là số integer nhị phân, biểu diễn giá trị tín hiệu. Nó được gọi là kiểu dấu phảy tĩnh. Tuy nhiên thuật ngữ "dấu phảy tĩnh" không cần nhắc tới nếu không có nhu cầu phân biệt.

Ví dụ ADC 16 bit nhị phân cho ra giá trị mã từ -16383 đến +16383, lỗi xấp xỉ tín hiệu là ≈10−5, đáp ứng tốt nhu cầu số hoá âm nhạc thông thường. Trong ứng dụng âm nhạc thì không cần quan tâm giá trị tuyệt đối phải là chính xác, nên việc thích ứng với cường độ âm thanh thực hiện bằng chỉnh chiết áp khuếch đại là đủ.

Trong đo lường hay ứng dụng cần giá trị chính xác, thì ADC này chỉ đáp ứng dải động xác định.

ADC dấu phẩy động

[sửa | sửa mã nguồn]Trong các thiết bị đo lường có dải động rộng thì sử dụng ADC dấu phảy động. Kiến trúc của ADC nầy gồm có hai phần:

- Tiền khuếch đại có độ khuếch điều khiển nhị phân, với số bit điều khiển là số bit đặc tính của kết quả.

- ADC dấu phảy tĩnh, có số bit chính là số bit định trị của kết quả.

Hoạt động của ADC nầy có hai kỳ. Kỳ 1, xác định bit đặc tính để tiền khuếch đại cho ra tín hiệu có độ lớn trong dải động của ADC chính, trong đó giá trị đặc tính cao thì độ khuếch thấp. Kỳ 2, ADC chính số hóa.

Các lỗi đặc trưng

[sửa | sửa mã nguồn]

- Đặc trưng biến đổi phi tuyến

- Trôi điểm không do trôi phông của các phần tử tuyến tính trong hay ngoài chip.

- Nhảy sai mức hiện ra ở dạng quá rộng hay quá cao, do ảnh hưởng nhiễu và dải bất định ở mức ngưỡng so sánh gây ra.

- Lỗi lệch thời hay "skew", xảy ra ở ADC ghép kênh. ADC ghép kênh phải tuần tự biến đổi cho các tín hiệu vào, nên tín hiệu vào được lấy mẫu không cùng thời điểm. Một số thiết bị đã bố trí microprocessor tính hiệu đính skew để đưa về cùng thời điểm.

- Lỗi Aliasing: khi bộ lọc cắt tần cao không đủ mạnh, các nhiễu tần số cao lọt vào.

Lấy mẫu lố (oversampling)

[sửa | sửa mã nguồn]Do công nghiệp chế tạo hiện cho ra ADC tốc độ nhanh và giá rẻ, nên chỉ tiêu tần số số hóa của chip thường cao hơn nhu cầu của mạch ứng dụng. Mặt khác, mạch ứng dụng thường thiết kế với nhiều nhịp số hóa chọn được. Nhằm khai thác tối đa năng lực ADC và tránh phải bố trí mạch lọc anti-alias cho mỗi mức nhịp số hóa, kỹ thuật Oversampling được vận dụng.

Nội dung của kỹ thuật Oversampling là, tín hiệu được số hóa ở tần cao hơn K lần tần yêu cầu làm việc, sau đó kết quả được xử lý bằng "kỹ thuật lọc số", rồi cộng chúng lại theo bước số hóa yêu cầu.[6]

Kết quả cộng cho ra độ phân giải cao hơn độ phân giải danh định ∆V của chip, ví dụ đạt được mức 20 bit bằng ADC 16 bit, tức là tăng 4 bit. Nếu cộng K số lại (cộng không có phủ chồng) thì gia tăng bit cao nhất là cỡ log2(K)/2, tuy nhiên độ phân giải thực tế bị chặn bởi độ rộng của dải bất định của comparator khi chuyển mức giữa hai mức kề nhau, và tùy thuộc chất lượng của chip sử dụng.[7] Điều này được giải thích như sau:

Trường hợp ADC lý tưởng thì ngưỡng lý tưởng phân biệt ra mức tín hiệu (L)∆V và (L+1)∆V nằm ở giữa. Trong thực tế comparator có lỗi bất định ở dải có độ rộng là δV, tức là giá trị tín hiệu rơi vào dải đó sẽ cho ra hoặc là L hoặc là L+1. Khi đó oversampling dùng chip có độ phân giải ∆V thì chỉ đạt độ phân giải cao nhất là cỡ δV. Đó là giới hạn tối đa lấy mẫu lố của kiểu chip xác định.

Oversampling gặp lỗi nếu quan sát tín hiệu DC hoặc biến đổi quá chậm, ví dụ tín hiệu DC vào ở mức (L + 0,7) ∆V, kết quả số hóa sẽ luôn là L+1, và Oversampling không tăng được cái gì cả. Để khắc phục thì người ta đưa vào một lượng nhiễu răng cưa nhỏ biết trước, và loại đi trong kết quả cộng.

Ứng dụng

[sửa | sửa mã nguồn]ADC là một trong những phần tử phổ biến, có mặt trong tất cả các thiết bị kỹ thuật số tiếp nhận thông tin từ các cảm biến analog. ADC cũng thường được tích hợp với cảm biến và đặt ngay tại đầu thu, truyền dữ liệu dạng số về khối xử lý. Nó đảm bảo sự ưu việt là dữ liệu trung thực, truyền đưa dễ dàng và xử lý thuận tiện.[8]

Các nhóm

[sửa | sửa mã nguồn]- ADC nhanh, dấu phảy tĩnh và số bit thấp, cỡ 8-12 bit, dùng cho biến đổi tín hiệu video, radar, cảm biến CCD,...

- ADC âm thanh, dấu phảy tĩnh và số bit trung bình, dùng trong thiết bị âm thanh.

- ADC kỹ thuật, dấu phảy tĩnh hoặc động, số bit cỡ 24-32, dùng trong thiết bị đo lường tín hiệu, ví dụ ADC 24-bit 2.5 MHz AD7760 Lưu trữ 2015-12-21 tại Wayback Machine.

- ADC đo lường đơn giản cho ra số BCD với 3-5 digit không kể dấu, ví dụ ICL7135. Một số chip tích hợp với mạch "giải mã 7 thanh" để hiện số bằng LED hay màn hiện LCD như ICL7106, ICL7107. Chúng được dùng trong máy đo thông dụng, như Multimeter hiện số, có bán ngoài chợ Nhật Tảo.

Lĩnh vực

[sửa | sửa mã nguồn]- Đo đạc trong vật lý, hóa học, sinh học, y học, đo lường điện,...

- Âm nhạc, hình ảnh, truyền hình truyền thông,...

- Thông tin liên lạc, thiết bị dân sinh,...

Flash ADC được tạo ra khá sớm, dùng cho hiện cường độ âm thanh bằng dãy LED trong máy hát nhạc, ví dụ IC LM3914.

Tham khảo

[sửa | sửa mã nguồn]- ^ Walden R. H., 1999. Analog-to-digital converter survey and analysis. IEEE Journal on Selected Areas in Communications 17 (4), p. 539–550. doi:10.1109/49.761034

- ^ a b “What is ADC - Analog to Digital Converters”. circuitdigest.com. Truy cập ngày 1 tháng 9 năm 2019.

- ^ S. J. Orfanidis, Introduction to Signal Processing, Prentice Hall Publisher 2010.

- ^ ADC and DAC Glossary - Maxim

- ^ “ADC Guide, Part 2: The Sample Rate” (PDF). Truy cập ngày 1 tháng 9 năm 2019.

- ^ Nauman Uppal (2004). "Upsampling vs. Oversampling for Digital Audio". Truy cập 2/12/2015.

- ^ "Improving ADC Resolution by Oversampling and Averaging". Silicon Laboratories Inc. Truy cập 2/12/2015.

- ^ Rudy J. van de Plassche: CMOS integrated analog-to-digital and digital-to-analog converters. 2nd edition. Kluwer Academic, Boston 2003, ISBN 1-4020-7500-6

Xem thêm

[sửa | sửa mã nguồn]Liên kết ngoài

[sửa | sửa mã nguồn]![[Sách] Những cô em gái - Nguyễn Nhật Ánh](https://down-ws-vn.img.susercontent.com/15910be8b1f00f27ed5c124482bcbcfd.webp) GIẢM

13%

GIẢM

13%

GIẢM

24%

GIẢM

24%

GIẢM

21%

GIẢM

21%

GIẢM

15%

GIẢM

15%

GIẢM

43%

GIẢM

43%

GIẢM

15%

GIẢM

15%