X86-64

x86-64 (còn gọi là x64, x86_64, AMD64 và Intel64) là phiên bản mở rộng 64bit của tập lệnh x86. Nó giới thiệu hai chế độ hoạt động mới, chế độ 64 bit và chế độ tương thích, cùng với chế độ phân trang 4 cấp độ mới. Với chế độ 64 bit và chế độ phân trang mới, nó hỗ trợ bộ nhớ ảo và bộ nhớ vật lý lớn hơn rất nhiều so với các phiên bản trước 32 bit, cho phép các chương trình lưu trữ lượng dữ liệu lớn hơn trong bộ nhớ. x86-64 cũng mở rộng các thanh ghi mục đích chung thành 64 bit, cũng như mở rộng số lượng của chúng từ 8 (một số trong đó có chức năng giới hạn hoặc cố định, ví dụ như để quản lý ngăn xếp) thành 16 (hoàn toàn chung) và cung cấp nhiều cải tiến khác. Các thao tác dấu phẩy động được hỗ trợ thông qua các nhóm lệnh giống như SSE2 bắt buộc và các thanh ghi kiểu x87/MMX thường không được sử dụng (nhưng vẫn khả dụng ngay cả ở chế độ 64 bit); thay vào đó, một bộ gồm 32 thanh ghi vector, mỗi thanh 128 bit, được sử dụng (Mỗi thanh có thể lưu một hoặc hai số kép hoặc một đến bốn số đơn hoặc các định dạng số nguyên khác nhau.) Trong chế độ 64 bit, các nhóm lệnh được sửa đổi để hỗ trợ toán hạng 64 bit và chế độ địa chỉ 64 bit. Chế độ tương thích cho phép các ứng dụng người dùng 16 và 32 bit chạy cùng tồn tại không thay đổi với các ứng dụng 64 bit nếu hệ điều hành 64 bit hỗ trợ chúng.[1][note 1] Vì các tập lệnh x86 16 bit và 32 bit đầy đủ vẫn được triển khai trong phần cứng mà không có bất kỳ mô phỏng can thiệp nào, các tệp thực thi cũ này có thể chạy với ít hoặc không có hình phạt hiệu năng,[3] trong khi các ứng dụng mới hơn hoặc được sửa đổi có thể tận dụng các tính năng mới của thiết kế bộ xử lý để đạt được cải tiến hiệu suất. Ngoài ra, bộ xử lý hỗ trợ x86-64 vẫn bật ở chế độ thực để tương thích ngược hoàn toàn

Thông số ban đầu, được tạo bởi AMD và phát hành năm 2000, đã được AMD, Intel và VIA triển khai. Bộ xử lý AMD K8 là bản đầu tiên thực hiện nó. Đây là sự bổ sung đáng kể đầu tiên cho kiến trúc x86 được thiết kế bởi một công ty khác ngoài Intel. Intel đã buộc phải tuân theo và giới thiệu một họ NetBurst đã được sửa đổi, tương thích với phần mềm với đặc điểm kỹ thuật của AMD. VIA Technologies giới thiệu x86-64 trong kiến trúc VIA Isaiah của họ, với VIA Nano.

Kiến trúc x86-64 khác với kiến trúc Intel Itanium (trước đây là IA-64), không tương thích ở cấp độ tập lệnh gốc với kiến trúc x86. Các hệ điều hành và ứng dụng được viết cho cái này không thể chạy trên cái kia.

AMD64

[sửa | sửa mã nguồn]

Lịch sử

[sửa | sửa mã nguồn]AMD64 được tạo ra để thay thế cho kiến trúc IA-64 hoàn toàn khác, được thiết kế bởi Intel và Hewlett Packard. Được công bố lần đầu vào năm 1999 [4] trong khi thông số kỹ thuật đầy đủ có sẵn vào tháng 8 năm 2000,[5] kiến trúc AMD64 được AMD định vị ngay từ đầu như một cách tiến hóa để thêm khả năng tính toán 64 bit vào kiến trúc x86 hiện tại, trái ngược với cách tiếp cận của Intel là tạo ra một cách hoàn toàn kiến trúc 64 bit mới với IA-64.

Bộ xử lý dựa trên AMD64 đầu tiên, Opteron, được phát hành vào tháng 4 năm 2003.

Triển khai

[sửa | sửa mã nguồn]Các bộ xử lý của AMD triển khai kiến trúc AMD64 bao gồm Opteron, Athlon 64, Athlon 64 X2, Athlon 64 FX, Athlon II (theo sau bởi "X2", "X3", hay "X4" để chỉ số lượng lõi và các mẫu XLT), Turion 64, Turion 64 X2, Sempron ("Palermo" E6 và tất cả các model "Manila"), Phenom (theo sau bởi "X3" hay "X4" để chỉ số lượng lõi), Phenom II (theo sau bởi "X2", "X3", "X4" hay "X6" để chỉ số lượng lõi), FX, Fusion/APU và Ryzen/Epyc.

Đặc điểm kiến trúc

[sửa | sửa mã nguồn]Đặc điểm xác định chính của AMD64 là sự sẵn có của các thanh ghi bộ xử lý đa năng 64 bit (ví dụ, rax và rbx), các phép toán số học và logic số nguyên 64 bit và các địa chỉ ảo 64 bit. Các nhà thiết kế đã nắm lấy cơ hội để thực hiện các cải tiến khác là tốt. Một số thay đổi quan trọng nhất được mô tả dưới đây.

- Khả năng tính toán 64-bit

- Tất cả các thanh ghi GPR được mở rộng từ 32 bits lên 64 bits, và tất cả các hoạt động số học và logic, hoạt động bộ nhớ vào thanh ghi và thanh ghi vào bộ nhớ, v.v., giờ đây có thể hoạt động trực tiếp trên các số nguyên 64 bit. Push và pop trên ngăn xếp mặc định thành các bước 8 byte và con trỏ rộng 8 byte.

- Đăng ký bổ sung

- Ngoài việc tăng kích thước của các thanh ghi GPR, số lượng các thanh ghi GPR tăng từ 8 (eax, ecx, edx, ebx, esp, ebp, esi, edi) trong x86 lên 16 (rax, rcx, rdx, rbx, rsp, rbp, rsi, rdi, r8, r9, r10, r11, r12, r13, r14, r15). Do đó, có thể giữ nhiều biến cục bộ hơn trong các thanh ghi thay vì trên ngăn xếp và để cho các thanh ghi giữ các hằng số truy cập thường xuyên; các đối số cho chương trình nhỏ và nhanh cũng có thể được truyền vào các thanh ghi ở mức độ lớn hơn. AMD64 vẫn có ít thanh ghi hơn so với nhiều bộ lệnh RISC (e.g. PA-RISC và MIPS có 32 GPR; Alpha, ARM 64-bit, và SPARC có 31) hoặc các máy tương tự VLIW như IA-64 (có 128 thanh ghi). Tuy nhiên, việc triển khai AMD64 có thể có nhiều thanh ghi bên trong hơn số lượng thanh ghi kiến trúc được hiển thị bởi tập lệnh. Ví dụ, lõi AMD Zen có 168 số nguyên 64 bit và 160 thanh ghi vật lý điểm nổi vector 128 bit.

- Thanh ghi bổ sung XMM (SSE)

- Tương tự, số lượng thanh ghi 128-bit XMM(được dùng cho nhóm lệnh Streaming SIMD) cũng được tăng từ 8 lên 16.

- Ngăn xếp thanh ghi x87 FPU truyền thống không được bao gồm trong phần mở rộng thanh ghi kích thước file ở chế độ 64 bit, so với các thanh ghi XMM được sử dụng bởi SSE2, đã được mở rộng. Ngăn xếp thanh ghi x87 không phải là một tệp đăng ký đơn giản mặc dù nó cho phép truy cập trực tiếp vào các thanh ghi riêng lẻ bằng các hoạt động trao đổi chi phí thấp.

- Không gian địa chỉ ảo lớn hơn

- Kiến trúc AMD64 định nghĩa định dạng địa chỉ ảo 64 bit, trong đó 48 bit thứ tự thấp được sử dụng trong các triển khai hiện tại.[1](tr120) Điều này cho phép nâng không gian địa chỉ ảo lên tối đa 256 TB (248 byte). Định nghĩa kiến trúc cho phép giới hạn này được nâng lên trong các triển khai trong tương lai tới 64 bit đầy đủ,[1](tr2)(tr3)(tr13)(tr117)(tr120) mở rộng không gian địa chỉ ảo lên 16 EB (264 byte). Điều này được so sánh với chỉ 4 GB (232 byte) của x86.[6] Điều này có nghĩa là các file rất lớn có thể được vận hành bằng cách ánh xạ toàn bộ tệp vào không gian địa chỉ của quy trình (thường nhanh hơn nhiều so với làm việc với các lệnh đọc/ghi file), thay vì phải ánh xạ các vùng của file vào và ra không gian địa chỉ.

- Không gian địa chỉ vật lý lớn hơn

- Việc triển khai ban đầu của kiến trúc AMD64 đã triển khai các địa chỉ vật lý 40 bit và do đó có thể quản lý tới 1 TB (240 byte) RAM.[1](tr24) Các triển khai hiện tại của kiến trúc AMD64 (bắt đầu từ kiến trúc vi mô AMD 10h) mở rộng điều này lên 48 bit địa chỉ vật lý[7] và do đó có thể quản lý tối đa 256 TB RAM. Kiến trúc cho phép mở rộng tới 52 bit trong tương lai [1](tr24)[8] (bị giới hạn bởi định dạng mục nhập bảng trang);[1](tr131) điều này sẽ cho phép quản lý tối đa 4 PB RAM. Để so sánh, bộ xử lý 32 bit x86 bị giới hạn ở 64 GB RAM ở chế độ Physical Address Extension (PAE),[9] hay 4GB RAM khi không ở chế độ PAE.[1](tr4)

- Không gian địa chỉ vật lý lớn hơn trong chế độ cũ

- Khi hoạt động ở chế độ cũ, kiến trúc AMD64 hỗ trợ chế độ Physical Address Extension (PAE), giống như hầu hết các bộ xử lý x86 hiện tại, nhưng AMD64 mở rộng PAE từ 36 bit đến giới hạn kiến trúc là 52 bit địa chỉ vật lý. Do đó, bất kỳ triển khai nào cũng cho phép giới hạn địa chỉ vật lý giống như trong long mode.[1](tr24)

- Con trỏ lệnh truy cập dữ liệu tương đối

- Các lệnh bây giờ có thể tham chiếu dữ liệu liên quan đến con trỏ lệnh (thanh ghi RIP). Điều này làm cho mã độc lập vị trí, như thường được sử dụng trong các thư viện dùng chung và mã được tải vào thời gian chạy, hiệu quả hơn.

- Tập lệnh SSE

- Kiến trúc AMD64 ban đầu đã sử dụng SSE và SSE2 của Intel làm tập lệnh cốt lõi. Các bộ hướng dẫn này cung cấp một bổ sung vectơ cho vô hướng x87 FPU,cho các kiểu dữ liệu có độ chính xác đơn và độ chính xác kép. SSE2 cũng cung cấp các phép toán vectơ số nguyên, cho các loại dữ liệu có độ chính xác từ 8 bit đến 64 bit. Điều này làm cho khả năng vectơ của kiến trúc ngang bằng với các bộ xử lý x86 tiên tiến nhất thời bấy giờ. Các tập lệnh này cũng có thể được sử dụng ở chế độ 32 bit. Sự phổ biến của bộ xử lý 64 bit đã làm cho các khả năng vectơ này trở nên phổ biến trong các máy tính gia đình, cho phép cải thiện các tiêu chuẩn của các ứng dụng 32 bit. Ví dụ, phiên bản 32 bit của Windows 8 yêu cầu sự hiện diện của các tập lệnh SSE2.[10] Bộ lệnh SSE3 và Streaming SIMD Extensions sau này không phải là các tính năng tiêu chuẩn của kiến trúc.

- No-Execute Bit

- No-Execute bit hay NX bit (bit 63 của bảng phân mục trang) cho phép hệ điều hành chỉ định trang nào của không gian địa chỉ ảo có thể chứa mã thực thi và không thể. Nỗ lực thực thi mã từ một trang được gắn thẻ "không thực thi" sẽ dẫn đến vi phạm quyền truy cập bộ nhớ, tương tự như nỗ lực ghi vào trang chỉ đọc. Điều này sẽ gây khó khăn hơn cho mã độc để kiểm soát hệ thống thông qua các cuộc tấn công "tràn bộ đệm" hoặc "bộ đệm không được kiểm soát". Một tính năng tương tự đã có sẵn trên các bộ xử lý x86 kể từ 80286 như một thuộc tính của bộ mô tả phân đoạn; Tuy nhiên, điều này chỉ hoạt động trên toàn bộ phân khúc tại một thời điểm. Địa chỉ được phân đoạn từ lâu đã được coi là một chế độ hoạt động lỗi thời và tất cả các hệ điều hành PC hiện tại có hiệu lực đều bỏ qua nó, đặt tất cả các phân đoạn thành địa chỉ cơ bản bằng 0 và (trong triển khai 32 bit của chúng) có kích thước 4GB. AMD là nhà cung cấp gia đình x86 đầu tiên thực hiện không thực thi trong chế độ địa chỉ tuyến tính. Tính năng này cũng có sẵn ở chế độ cũ trên bộ xử lý AMD64 và bộ xử lý Intel x86 gần đây, khi PAE được sử dụng.

- Loại bỏ các tính năng cũ

- Một vài tính năng "lập trình hệ thống" của kiến trúc x86 không được sử dụng hoặc sử dụng trong các hệ điều hành hiện đại và không có sẵn trên AMD64 ở chế độ dài (64 bit và tương thích) hoặc chỉ tồn tại ở dạng hạn chế. Chúng bao gồm địa chỉ được phân đoạn (mặc dù các phân đoạn FS và GS được giữ lại ở dạng tiền đình để sử dụng làm con trỏ cơ sở bổ sung cho cấu trúc hệ điều hành),[1](tr70) cơ chế chuyển đổi trạng thái tác vụ và chế độ 8086 ảo. Các tính năng này vẫn được triển khai đầy đủ trong "legacy mode", cho phép các bộ xử lý này chạy các hệ điều hành 32 bit và 16 bit mà không cần sửa đổi. Một số hướng dẫn hiếm khi hữu ích không được hỗ trợ trong chế độ 64 bit, bao gồm lưu/khôi phục các thanh ghi phân đoạn trên ngăn xếp, lưu / khôi phục tất cả các thanh ghi (PUSHA/POPA), số học thập phân, hướng dẫn BOUND và INTO và nhảy xa và gọi với toán hạng ngay lập tức.

Chi tiết không gian địa chỉ ảo

[sửa | sửa mã nguồn]Địa chỉ mẫu Canonical

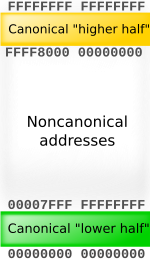

[sửa | sửa mã nguồn]Mặc dù địa chỉ ảo rộng 64 bit ở chế độ 64 bit, nhưng việc triển khai hiện tại (và tất cả các chip được biết là đang trong giai đoạn lập kế hoạch) không cho phép sử dụng toàn bộ không gian địa chỉ ảo 264 bytes (16 EB). Con số này sẽ gấp khoảng bốn tỷ lần kích thước của không gian địa chỉ ảo trên các máy 32 bit. Hầu hết các hệ điều hành và ứng dụng sẽ không cần một không gian địa chỉ lớn như vậy trong tương lai gần, do đó, việc triển khai các địa chỉ ảo rộng như vậy chỉ đơn giản là làm tăng sự phức tạp và chi phí dịch địa chỉ mà không có lợi ích thực sự. Do đó, AMD đã quyết định rằng, trong lần triển khai đầu tiên của kiến trúc, chỉ có 48 bit quan trọng nhất của một địa chỉ ảo thực sự sẽ được sử dụng trong dịch địa chỉ (tra cứu bảng trang).[11](tr120)

Ngoài ra, đặc tả AMD yêu cầu 16 bit quan trọng nhất của bất kỳ địa chỉ ảo nào, các bit 48 đến 63, phải là bản sao của bit 47 (theo cách gần giống với ký hiệu mở rộng). Nếu yêu cầu này không được đáp ứng, bộ xử lý sẽ đưa ra một ngoại lệ.[11](tr131) Địa chỉ tuân thủ quy tắc này được gọi là "mẫu canonical."[11](tr130) Địa chỉ dạng Canonical chạy từ 0 đến 00007FFF'FFFFFFFF, và từ FFFF8000'00000000 đến FFFFFFFF'FFFFFFFF, với tổng số 256TB không gian địa chỉ ảo có thể sử dụng. Con số này vẫn lớn hơn 65.536 lần so với không gian địa chỉ 4GB ảo của các máy 32 bit.

Tính năng này giúp giảm khả năng mở rộng sau này thành địa chỉ 64 bit thực sự. Nhiều hệ điều hành (bao gồm, nhưng không giới hạn ở họ Windows NT) tự lấy một nửa không gian địa chỉ (địa chỉ kernel) có địa chỉ cao hơn và để lại một nửa địa chỉ thấp hơn (không gian người dùng) cho mã ứng dụng, chế độ người dùng ngăn xếp, đống, và các vùng dữ liệu khác.[12] Thiết kế "địa chỉ canonical" đảm bảo rằng mọi triển khai tuân thủ AMD64 đều có hai nửa bộ nhớ, nửa dưới bắt đầu từ 00000000'00000000 và "tăng lên" khi có nhiều bit địa chỉ ảo hơn, trong khi nửa cao hơn được "neo" đến đỉnh của không gian địa chỉ và mở rộng xuống dưới. Ngoài ra, việc triển khai " kiểu canonical" của các địa chỉ bằng cách kiểm tra các bit địa chỉ không được sử dụng sẽ ngăn hệ điều hành sử dụng chúng trong các con trỏ được gắn thẻ như cờ, đánh dấu đặc quyền, v.v. địa chỉ bit.

Các phiên bản Windows đầu tiên cho x64 thậm chí không sử dụng đủ 256 TB; chúng bị giới hạn chỉ 8 TB không gian người dùng và 8 TB không gian kernel.[12] Windows không hỗ trợ toàn bộ không gian địa chỉ 48 bit cho đến Windows 8.1, được phát hành vào tháng 10 năm 2013.[12]

Cấu trúc bảng trang

[sửa | sửa mã nguồn]Chế độ địa chỉ 64 bit ("long mode") là Physical Address Extensions (PAE); do đó, kích thước trang có thể là 4 KB (212 bytes) hay 2 MB (221 bytes).[11](tr120) Long mode ũng hỗ trợ kích thước trang là 1 GB (230 bytes).[11](tr120) Rather than the three-level page table system used by systems in PAE mode, systems running in long mode use four levels of page table: PAE's Page-Directory Pointer Table is extended from four entries to 512, and an additional Page-Map Level 4 (PML4) Table is added, containing 512 entries in 48-bit implementations.[11](tr131) A full mapping hierarchy of 4 KB pages for the whole 48-bit space would take a bit more than 512 GB of memory (about 0.195% of the 256 TB virtual space).

Intel đã đề xuất một sơ đồ với bảng trang năm cấp. Nếu được triển khai, điều này sẽ cho phép bộ xử lý Intel 64 hỗ trợ không gian địa chỉ ảo 57 bit.[13]

Giới hạn hệ điều hành

[sửa | sửa mã nguồn]Hệ điều hành cũng có thể giới hạn không gian địa chỉ ảo. Chi tiết, nếu có, được đưa ra trong phần "Đặc điểm và tính tương thích của hệ điều hành".

Chi tiết không gian địa chỉ vật lý

[sửa | sửa mã nguồn]Bộ xử lý AMD64 hiện tại hỗ trợ không gian địa chỉ vật lý lên tới 248 bytes RAM, hay 256 TB.[7] Tuy nhiên, tính đến tháng 6 năm 2010[cập nhật], không có bo mạch chủ x86-64 nào hỗ trợ RAM 256 TB.[14][15][16][17] Hệ điều hành có thể đặt giới hạn bổ sung cho dung lượng RAM có thể sử dụng hoặc được hỗ trợ. Chi tiết về điểm này được đưa ra trong phần "Đặc điểm và tính tương thích của hệ điều hành" của bài viết này.

Intel 64

[sửa | sửa mã nguồn]Intel 64 là triển khai x86-64 của Intel, được sử dụng và triển khai trong các bộ xử lý khác nhau do Intel sản xuất.

Lịch sử

[sửa | sửa mã nguồn]Trong lịch sử, AMD đã phát triển và sản xuất các bộ xử lý với các bộ hướng dẫn được thiết kế theo thiết kế ban đầu của Intel, nhưng với x86-64, các vai trò đã bị đảo ngược: Intel thấy mình ở vị trí chấp nhận ISA mà AMD đã tạo ra như một phần mở rộng cho dòng bộ xử lý x86 của Intel.

Dự án của Intel ban đầu có tên mã là Yamhill (theo tên sông [./https://en.wikipedia.org/wiki/Yamhill_River Yamhill] ở thung lũng Willamette, Oregon).[cần dẫn nguồn] Sau vài năm phủ nhận sự tồn tại của mình, Intel đã tuyên bố tại IDF tháng 2 năm 2004 rằng dự án thực sự đang được tiến hành. Chủ tịch của Intel tại thời điểm đó, Craig Barrett, thừa nhận rằng đây là một trong những bí mật được giữ kín nhất của họ.[18][19]

Tên của Intel cho tập lệnh này đã thay đổi nhiều lần. Tên được sử dụng tại IDF là CT (có lẽ là Clackamas Technology, một tên mã khác từ một dòng sông ở Oregon); trong vài tuần, họ bắt đầu gọi nó là IA-32e (nghĩa là bản mở rộng của IA-32) và vào tháng 3 năm 2004 đã tiết lộ tên "chính thức" EM64T (Extended Memory 64 Technology). Cuối năm 2006, Intel bắt đầu sử dụng tên Intel 64 để triển khai, song song với việc AMD sử dụng tên AMD64.[20]

Bộ xử lý đầu tiên triển khai Intel 64 là bộ xử lý đa socket Xeon tên mã Nocona vào tháng 6 năm 2004, Ngược lại, các chip Prescott ban đầu (tháng 2 năm 2004) không kích hoạt tính năng này. Intel sau đó đã bắt đầu bán Pentium 4s hỗ trợ Intel 64 bằng cách sử dụng bản sửa đổi E0 của lõi Prescott, được bán trên thị trường OEM với tên Pentium 4, model F. Bản sửa đổi E0 cũng thêm eXecute Disable (XD) (tên của Intel cho bit NX) cho Intel 64 và đã được đưa vào Xeon hiện tại có tên mã là Irwindale. Intel chính thức ra mắt Intel 64 (dưới tên EM64T tại thời điểm đó) trong các bộ xử lý máy tính để bàn chính là N0 bước Prescott-2M.

Bộ xử lý di động Intel đầu tiên triển khai Intel 64 là phiên bản [./https://en.wikipedia.org/wiki/Merom_(microprocessor) Merom] của bộ xử lý Core 2, được phát hành vào ngày 27 tháng 7 năm 2006. Không có CPU máy tính xách tay nào trước đây của Intel (Core Duo, Pentium M, Celeron M, Mobile Pentium 4) triển khai Intel 64.

Triển khai

[sửa | sửa mã nguồn]Các bộ xử lý của Intel triển khai kiến trúc Intel64 bao gồm các dòng Pentium 4 F-series / 5x1, 506 và 516, các mẫu Celeron D 3x1, 3x6, 355, 347, 352, 360 và 365 và tất cả các mẫu Celerons sau này, tất cả các mẫu của Xeon kể từ " Nocona ", Atom 230, 330, D410, D425, D510, D525, N450, N455, N470, N475, N550, N570, N2600 và N2800, tất cả phiên bản của Pentium D, Pentium Extreme Edition, Core 2, Core i9, Core i7, Core i5, và Core i3, và dòng vi xử lý Xeon Phi 7200.

Triển khai X86-64 của VIA

[sửa | sửa mã nguồn]VIA Technologies đã giới thiệu triển khai đầu tiên của họ về kiến trúc x86-64 vào năm 2008 sau năm năm phát triển bởi bộ phận, Centaur Technology.[21] Tên mã "Isaiah", kiến trúc 64 bit được công bố vào ngày 24 tháng 1 năm 2008,[22] và ra mắt vào ngày 29 tháng 5 dưới tên thương hiệu VIA Nano.[23]

Bộ xử lý hỗ trợ một số phần mở rộng x86 dành riêng cho VIA được thiết kế để tăng hiệu quả trong các thiết bị năng lượng thấp. Dự kiến kiến trúc Isaiah sẽ có hiệu suất số nguyên nhanh gấp hai lần và nhanh gấp bốn lần hiệu suất điểm nổi so với VIA Esther thế hệ trước với tốc độ xung nhịp tương đương. Mức tiêu thụ năng lượng cũng được dự kiến sẽ ngang bằng với các CPU VIA thế hệ trước, với công suất thiết kế nhiệt dao động từ 5 W đến 25 W.[24] Là một thiết kế hoàn toàn mới, kiến trúc Isaiah được xây dựng với sự hỗ trợ cho các tính năng như thiết lập x86-64 và ảo hóa x86 không khả dụng trên các phiên bản trước, dòng VIA C7, trong khi vẫn giữ lại các phần mở rộng mã hóa của chúng.

Giấy phép

[sửa | sửa mã nguồn]x86-64/AMD64 chỉ được phát triển bởi AMD. AMD giữ bằng sáng chế về các kỹ thuật được sử dụng trong AMD64;[25][26][27] những bằng sáng chế đó phải được cấp phép từ AMD để triển khai AMD64. Intel đã ký một thỏa thuận cấp phép chéo với AMD, cấp phép cho AMD bằng sáng chế của họ về các kỹ thuật x86 hiện có và cấp phép từ AMD bằng sáng chế của họ về các kỹ thuật được sử dụng trong x86-64.[28] Năm 2009, AMD và Intel đã giải quyết một số vụ kiện và bất đồng về cấp phép chéo, mở rộng các thỏa thuận cấp phép chéo của họ.[29][30][31]

Xem thêm

[sửa | sửa mã nguồn]Ghi chú

[sửa | sửa mã nguồn]- ^ In practice, 64-bit operating systems generally do not support 16-bit applications, although modern versions of Microsoft Windows contain a limited workaround that effectively supports 16-bit InstallShield and Microsoft ACME installers by silently substituting them with 32-bit code.[2]

Tham khảo

[sửa | sửa mã nguồn]- ^ a b c d e f g h i AMD Corporation (tháng 12 năm 2016). “Volume 2: System Programming” (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. Truy cập ngày 25 tháng 3 năm 2017.

- ^ Raymond Chen (ngày 31 tháng 10 năm 2013). “If there is no 16-bit emulation layer in 64-bit Windows, how come certain 16-bit installers are allowed to run?”.

- ^ IBM Corporation (ngày 6 tháng 9 năm 2007). “IBM WebSphere Application Server 64-bit Performance Demystified” (PDF). tr. 14. Bản gốc (PDF) lưu trữ ngày 25 tháng 1 năm 2022. Truy cập ngày 9 tháng 4 năm 2010.

Figures 5, 6 and 7 also show the 32-bit version of WAS runs applications at full native hardware performance on the POWER and x86-64 platforms. Unlike some 64-bit processor architectures, the POWER and x86-64 hardware does not emulate 32-bit mode. Therefore applications that do not benefit from 64-bit features can run with full performance on the 32-bit version of WebSphere running on the above mentioned 64-bit platforms.

- ^ “AMD Discloses New Technologies At Microporcessor Forum” (Thông cáo báo chí). AMD. ngày 5 tháng 10 năm 1999. Bản gốc lưu trữ ngày 8 tháng 3 năm 2012. Truy cập ngày 9 tháng 11 năm 2010.

- ^ “AMD Releases x86-64 Architectural Specification; Enables Market Driven Migration to 64-Bit Computing” (Thông cáo báo chí). AMD. ngày 10 tháng 8 năm 2000. Bản gốc lưu trữ ngày 8 tháng 3 năm 2012. Truy cập ngày 9 tháng 11 năm 2010.

- ^ “Intel 64 and IA-32 Architectures Software Developer's Manual, Volume 3A: System Programming Guide, Part 1” (PDF). tr. 4–10. Truy cập ngày 29 tháng 5 năm 2010.

- ^ a b “BIOS and Kernel Developer's Guide (BKDG) For AMD Family 10h Processors” (PDF). tr. 24. Truy cập ngày 27 tháng 2 năm 2016.

Physical address space increased to 48 bits.

- ^ “Myth and facts about 64-bit Linux” (PDF). ngày 2 tháng 3 năm 2008. tr. 7. Bản gốc (PDF) lưu trữ ngày 10 tháng 10 năm 2010. Truy cập ngày 30 tháng 5 năm 2010.

Physical address space increased to 48 bits

- ^ Shanley, Tom (1998). Pentium Pro and Pentium II System Architecture. PC System Architecture Series . Addison-Wesley. tr. 445. ISBN 0-201-30973-4.

- ^ Microsoft Corporation. “What is PAE, NX, and SSE2 and why does my PC need to support them to run Windows 8 ?”. Truy cập ngày 19 tháng 3 năm 2013.

- ^ a b c d e f AMD Corporation (tháng 12 năm 2016). “Volume 2: System Programming” (PDF). AMD64 Architecture Programmer's Manual. AMD Corporation. Truy cập ngày 25 tháng 3 năm 2017.

- ^ a b c “Memory Limits for Windows Releases”. MSDN. Microsoft. ngày 16 tháng 11 năm 2013. Truy cập ngày 20 tháng 1 năm 2014.

- ^ “5-Level Paging and 5-Level EPT” (PDF). Intel. tháng 5 năm 2017. Truy cập ngày 17 tháng 6 năm 2017.

- ^ “Opteron 6100 Series Motherboards”. Supermicro Corporation. Truy cập ngày 22 tháng 6 năm 2010.

- ^ “Supermicro XeonSolutions”. Supermicro Corporation. Truy cập ngày 20 tháng 6 năm 2010.

- ^ “Opteron 8000 Series Motherboards”. Supermicro Corporation. Truy cập ngày 20 tháng 6 năm 2010.

- ^ “Tyan Product Matrix”. MiTEC International Corporation. Truy cập ngày 21 tháng 6 năm 2010.

- ^ “Craig Barrett confirms 64 bit address extensions for Xeon. And Prescott”. The Inquirer. ngày 17 tháng 2 năm 2004. Bản gốc lưu trữ ngày 12 tháng 1 năm 2013. Truy cập ngày 16 tháng 2 năm 2019.

- ^ “"A Roundup of 64-Bit Computing", from internetnews.com”. Bản gốc lưu trữ ngày 25 tháng 9 năm 2012. Truy cập ngày 16 tháng 2 năm 2019.

- ^ “Intel 64 Architecture”. Intel. Truy cập ngày 29 tháng 6 năm 2007.

- ^ “VIA to launch new processor architecture in 1Q08” (subscription required). DigiTimes. Truy cập ngày 25 tháng 7 năm 2007.

- ^ Stokes, Jon (ngày 23 tháng 1 năm 2008). “Isaiah revealed: VIA's new low-power architecture”. Ars Technica. Truy cập ngày 24 tháng 1 năm 2008.

- ^ “VIA Launches VIA Nano Processor Family” (Thông cáo báo chí). VIA. ngày 29 tháng 5 năm 2008. Truy cập ngày 25 tháng 5 năm 2017.

- ^ “VIA Isaiah Architecture Introduction” (PDF). VIA. ngày 23 tháng 1 năm 2008. Bản gốc (PDF) lưu trữ ngày 7 tháng 9 năm 2008. Truy cập ngày 31 tháng 7 năm 2013.

- ^ Bản mẫu:Patent

- ^ Bản mẫu:Patent

- ^ Bản mẫu:Patent

- ^ “Patent Cross License Agreement Between AMD and Intel”. ngày 1 tháng 1 năm 2001. Bản gốc lưu trữ ngày 21 tháng 6 năm 2007. Truy cập ngày 23 tháng 8 năm 2009.

- ^ “AMD Intel Settlement Agreement”.

- ^ Stephen Shankland and Jonathan E. Skillings (ngày 12 tháng 11 năm 2009). “Intel to pay AMD $1.25 billion in antitrust settlement”. CNET. Bản gốc lưu trữ ngày 8 tháng 11 năm 2012. Truy cập ngày 24 tháng 4 năm 2012.

- ^ Smith, Ryan (ngày 12 tháng 11 năm 2009). “AMD and Intel Settle Their Differences: AMD Gets To Go Fabless”. AnandTech. Bản gốc lưu trữ ngày 13 tháng 5 năm 2010.

Liên kết ngoài

[sửa | sửa mã nguồn]- AMD Developer Guides, Manuals & ISA Documents

- x86-64: Extending the x86 architecture to 64-bits – technical talk by the architect of AMD64 (video archive), and second talk by the same speaker (video archive)

- AMD's "Enhanced Virus Protection"

- Intel tweaks EM64T for full AMD64 compatibility

- Analyst: Intel Reverse-Engineered AMD64

- Early report of differences between Intel IA32e and AMD64

- Porting to 64-bit GNU/Linux Systems, by Andreas Jaeger from GCC Summit 2003. An excellent paper explaining almost all practical aspects for a transition from 32-bit to 64-bit.

- Tech Report article: 64-bit computing in theory and practice Lưu trữ 2007-08-09 tại Wayback Machine

- Intel 64 Architecture

- Intel Software Network: "64 bits"

- TurboIRC.COM tutorial of entering the protected and the long mode the raw way from DOS Lưu trữ 2008-09-20 tại Wayback Machine

- Seven Steps of Migrating a Program to a 64-bit System

- Memory Limits for Windows Releases

GIẢM

49%

GIẢM

49%

![[Sách] Những cô em gái - Nguyễn Nhật Ánh](https://down-ws-vn.img.susercontent.com/15910be8b1f00f27ed5c124482bcbcfd.webp) GIẢM

13%

GIẢM

13%

GIẢM

13%

GIẢM

13%

GIẢM

37%

GIẢM

37%

GIẢM

47%

GIẢM

47%

GIẢM

30%

GIẢM

30%