80386

| << Intel 80386 >> Цэнтральны працэсар | |

Мікрапрацэсар Intel 80386 | |

| Вытворчасць: | з 17 кастрычніка 1985 па верасень 2007[1][2] |

| Вытворцы: | |

| Частата ЦП: | 12—40 МГц |

| Тэхналогія вытворчасці: |

1.5—1.0 мкм |

| Наборы інструкцый: | x86 |

| Раздым: | PGA132, PQFP132, TQFP144 |

Intel 80386 (таксама вядомы як i386 ці проста 386) — 32-бітны x86-сумяшчальны працэсар трэцяга пакалення фірмы Intel, прэзентаваны 17 кастрычніка 1985 года. Гэты працэсар быў першым 32-разрадным працэсарам для IBM PC-сумяшчальных ПК. Выкарыстоўваўся пераважна ў настольных і партатыўных ПК. У цяперашні час пераважна ўжываецца ў кантролерах, а таксама ў бытавой тэхніцы.

Апісанне

[правіць | правіць зыходнік]

Працэсар i386 цалкам сумяшчальны са сваімі папярэднікамі — працэсарамі 8086—80286. Ён выконвае праграмы, прызначаныя для іх, без патрэбы мадыфікацыі кода і перакампіляцыі (ці з мінімальнымі мадыфікацыямі) і робіць гэта больш эфектыўна:

- затрачвае на выкананне меншую колькасць тактаў сінхраніхацыі;

- мае вышэйшыя тактавыя частоты, за кошт ужывання новых тэхналогій;

- мае буйнейшы, у параўнанні з папярэднімі працэсарамі, буфер перадвыбаркі каманд — 16 байт (якіх хапае прыкладна на пяць каманд); буфер перадвыбаркі забяспечвае меншую колькасць звяртанняў за камандамі і выключаюць лішнія звяртанні ў памяць у кароткіх цыклах ды выкананні радковых каманд.

Разам з тым i386 з’яўляецца сур'ёзнай перапрацоўкай працэсара 80286. Паводле некаторых ацэнак, ні перад, ні пасля i386 архітэктура працэсараў x86 а ні разу не перапрацоўвала гэтак кардынальна. У працэсарах гэтай архітэктуры ўпершыню былі ўведзены асноўныя механізмы падтрымкі сучасных 32-разрадных аперацыйных сістэм для PC-сумяшчальных платформаў.

Асноўныя змены:

32 біты

[правіць | правіць зыходнік]Уся архітэктура x86 была пашырана да 32 біт — усе рэгістры (за выключэннем сегментных) сталі 32-бітнымі, атрымаўшы ў назве прэфікс «E» (EAX, EBX, EIP, EFLAGS і г. д.), з захаваннем поўнага набору каманд для працы з імі. У тым ліку:

- рэгістр флагаў атрымаў мноства новых флагаў для кіравання шматзадачнасцю

- гэгістр кіравання працэсарам MSW працэсара 80286, названы ў i386 «CR0»

32-бітнай стала і адрасацыя ў абароненым рэжыме (з магчымасцю стварэння 16-бітных сегментаў, для сумяшчальнасці з 80286). Яна дазволіла ўпершыню з часу з’яўлення 8086 забыцца на сегментацыю, а дакладней пра абмежаванне памера сегмента 64 кілабайты (абмежаванне 16-бітнага адраса), якое даўно перастала задавальняць праграмістаў.

Да з’яўлення i386 праграмы і аперацыйныя сістэмы выкарыстоўвалі некалькі галоваломных мадэляў арганізацыі памяці (драбнюткая — tiny, малая — small, вялікая — large, велізарная — huge), якія адрозніваліся арганізацыяй у памяці сегментаў коду, стэку і даных. 32-бітны адрас дазволіў ужываць замест іх адну простую плоскую мадэль (англ.: flat) — 32-бітны варыянт драбнюткай мадэлі, у якой усе сегменты задачы знаходзяцца ў адной адраснай прасторы. Плоская мадель забяспечвае памер такога «агульнага» сегмента да амаль 4 гігабайт, якіх на той час хапала для любой уяўнай задачы.

Плоская мадэль мае і недахопы:

- у ёй з’яўляюцца праблемы перасоўвальнасці машыннаго коду, якія раней лёгка абыходзіліся сегментацыяй, забеспячэнне перасоўвальнасці перайшло пад адказнасць аперацыйных сістэм, з новымі фарматамі дыскавага вобразу праграмы.

- плоская мадэль практычна скасоўвае кіраванне памяццю ў абароненым рэжыме (абмежаванне доступу і падтрымка віртуальнай памяці), якое да i386 магло выконвацца толькі на ўзроўні сегментацыі. Толькі з’яўленне новай мадэлі кіравання памяццю — старонкавай трансляцыі — забяспечыла плоскай мадэлі яе сённяшнюю папулярнасць.

Плоская мадэль увайшла ва ўжытак настолькі шырока, што сучасныя праграмісты нават і не падазраюць, што праграмы звяртаюцца ў памяць праз сегменты.

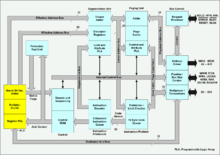

У i386 быў уведзены новы механізм кіравання памяццю — адрасная прастора, да якой звяртаецца працэсар за данымі і кодам, у якой змяшчаюцца сегменты (названая лінейнай адраснай прасторай) можа не адпавядаць рэальнай фізічнай памяці. Фізічная памяць (уключаючы буферы вонкавых прыладаў, напрыклад відэабуфер) можа быць транслявана ў лінейную адрасную прастору адвольным чынам — кожная старонка (памерам 4 кілабайты) лінейнай прасторы можа быць пераадрасавана на любую старонку фізічнай памяці праз каталог старонак, які знаходзцца ў аператыўнай памяці (адрас каталогу старонак задаецца значэннем новага регістра кіравання «CR3»).

Як і сегменты, старонкі лінейнай адраснай прасторы могуць быць аб’яўлены адсутнымі (звяртанне да такіх старонак выклікае апрацоўнік старонкавага парушэння аперацыйнай сістэмы). Адсутныя старонкі у першую чаргу выкарыстоўваюцца для арганізацыі віртуальнай памяці — апрацоўнік старонкавага парушэння здзяйсняе swapping старонак памяці з вонкавымі запамінальнымі прыладамі. Таксама адсутныя старонкі ўжываюцца ў плоскай мадэлі памяці (дзе памер сегмента звычайна мае памер ад 2 да 4 гігабайт, нават калі ў камп’ютара няма столькі фізічнай памяці) для маркіроўкі старонак сегменту, у якія аперацыйная сістэма не выдаткавала памяці. У гэтым выпадку старонкавае парушэнне звычайна завяршае задачу альбо пачынае яе адладку.

Праз старонкавую трансляцыю i386 можа адрасаваць да 4 Гбайт фізічнай памяці і да 64 Тбайт віртуальнай памяці.

Палепшаная падтрымка шматзадачнасці і абароны

[правіць | правіць зыходнік]Падтрымка шматзадачнасці ў працэсарах x86 значыць апаратную падтрымку «празрыстага» пераключэння з адной звычайнай праграмы (задачы) на іншую. Пры пераключэнні працэсар захоўвае свой стан (уключаючы адрас наступнай каманды, селектары сегментаў) у сегменце стану (TSS; сегмент памяці, з селектарам з рэгістра TR) адной задачы, пасля чаго ўзнаўляе стан іншай задачы з яе сегмента стану (селектар сегмента стану новай задачы загружаецца з дэскрыптара яе сегмента кода).

Пераключэнне паміж задачамі звычайна ажыццяўляецца:

- перарываннем таймера; час, на які наладкаваны таймер, завецца квантам часу для задачы

- сістэмным выклікам (выклікам функцыі аперацыйнай сістэмы)

- выключэннем — напрыклад, пры спробе выканаць недапушчальную команду ці звяртанні да адсутнай памяці

- адладкай

У i386 механізмы абароны і шматзадачнасці былі значна пашыраны і палепшаны. У залежнасці ад характару парушэнняў, яны могуць ціха ігнаравацца (напрыклад, некаторыя біты рэгістра EFLAGS нельга змяніць загрузкай флагаў са стэка), выклікаць апрацоўнік выключэння (аперацыйнай сістэмы). Сур'ёзная памылкі на ўзроўні аперацыйнай сістэмы (альбо ў рэальным рэжыме) могуць перавесці працэсар у рэжым аварыйнага спынення (напрыклад, пры парушэнні ў апрацоўніку падвойнага парушэння), з якога можна выйсці толькі апаратным скідам (англ.: reset) працэсара.

Напрыклад, i386 падтрымлівае абмежаванне доступу да портаў уводу-вываду і флага забароны перапыненняў праз:

- прызначэнне патрэбнага ўзроўню прывілеяў для выканання такіх каманд (двухбітным полем IOPL регістра флагаў)

- дазволам задачы выбарачнага доступу да портаў уводу-вываду праз бітавую маску ў сегменцк стану задачы

Спроба выканання недазволенай каманды ўводу-вываду здзяйсняе выключэнне, апрацоўнік якога (належыць аперацыйнай сістэме) можа завяршыць задачу праз памылку, ігнараваць (узнавіць выкананне з наступнай каманды) ці эмуляваць увод-вывад.

Акрамя таго шматзадачнасць i386 цалкам падтрымлівае ўсе новыя магчымасці — для 32-бітных задач сегмент стану змяшчае ўсе 32-бітныя і патрэбныя новыя рэгістры (напрыклад рэгістр CR3 з адрасам каталога старонак для гэтай задачы).

Віртуальны рэжым

[правіць | правіць зыходнік]У працэсары i386 кампанія Intel улічыла патрэбу паляпшэння падтрымкі рэальнага рэжыму, таму што праграмнае забеспячэнне ў час яго з’яўлення не было гатовым цалкам працаваць у абароненым рэжыме. Таму ў i386 магчыма пераключэнне з абароненага рэжыма назад у рэальны (пры распрацоўцы 80286 лічылася, што гэта не спатрэбіцца, таму на камп’ютарах з працэсарам 80286 вяртанне ў рэальны рэжым ажыццяўляецца схемна — праз скід працэсара).

У якасці пашыранай падтрымкі рэальнага рэжыма, i386 дазваляе адной ці некалькім задачам працаваць у віртуальным рэжыме — рэжыме эмуляцыі рэжыма рэальнага адраса.

Важна разумець што «віртуальны рэжым», нягледзячы на падабенства назвы з’яўляецца не «трэцім рэжымам працы працэсара» (то бок рэальны, абаронены і віртуальны), а толькі рэжымам працы задачы ў шматзадачным асяроддзі абароненага рэжыма.

Віртуальны рэжым прызначаны для адначасовага выконвання праграм рэальнага рэжыма (напрыклад, праграмы для DOS) у шматзадачнай аперацыйнай сістэме абароненага рэжыма.

Выкананне ў віртуальным рэжыме амаль ідэнтычна рэальнаму, за некалькімі выключэннямі, абумоўленымі тым, што віртуальная задача выконваецца ў абароненым рэжыме:

- віртуальная задача не можа выконваць прывілеяваныя каманды, таму што мае ніжэйшы ўзровень прывілеяў

- усе перапыненні і выключэнні апрацоўваюцца аперацыйнай сістэмай абароненага рэжыма (якая між тым можа ініцыяваць апрацоўнік перапынення віртуальнай задачы)

разам з тым, у задачы віртуальнага рэжыма можна выкарыстоўваць:

- старонкавае трансляваннне, напрыклад, для:

- пашырэння памяці, шляхам уключэння старонак у неўжываную адрасную прастору

- эмуляцыі пашырэнняў з пераключэннем банкаў (напрыклад, EMS-памяці)

- віртуальнай разгорткі ці згорткі буфераў вонкавых прылад (відэапамяць, апаратная EMS-памяць)

- эмуляцыі вонкавых прылад праз эмуляцыю портаў уводу-вываду

- адладка

- пры выкананні некалькіх задач віртуальнага рэжыма кожная з іх можа выконвацца алкам асобна адна ад адной, чаго нельга дасягнуць у рэальным рэжыме.

Напрыклад, пачынаючы з версій 4.01 — 5.0, пры ўжыванні менэджэра памяці EMM386 (і яго аналагаў іншых распрацоўнікаў) аперацыйная сістэма MS-DOS працуе як задача ў віртуальным рэжыме. EMM386 у гэтым выпадку з’яўляецца падабенствам аперацыйнай сістэмы абароненага рэжыма (перадаючы большасць сістэмных перапыненняў ядру MS-DOS у віртуальнай задачы).

Рэжым віртуальнага 8086 падтрымліваецца і ў наступных 32-бітных працэсарах x86, аж да рэжыма сумяшчальнасці ў x86-64.

Апаратная адладка

[правіць | правіць зыходнік]Як і ў папярэдніх працэсарах (пачынаючы з 8086), адладка ў i386 ажыццяўляецца выклікам адладкавага перапынення, апрацоўнік якога перадае кіраванне праграме-адладніку. У папярэдніх працэсарах адладка магла быць выклікана двума падзеямі:

- пакрокавае выканенне

- праграмныя пункты спынення

у i386 адладку таксама могуць пачаць:

- апаратныя пункты спынення

- пастка пераключэння задачы

Пакрокавае выканенне

[правіць | правіць зыходнік]Пакрокавае выкананне ці трасіроўка (выклік адладкавага перапынення пасля выканання кожнай каманды пры ўсталяваным флагу TF) у i386 засталося такім жа як і ў папярэдніх працэсарах, і працуе ва ўсіх новых рэжымах (32-бітнай адрасацыі і рэжыме віртуальнай задачы).

Пункты спынення

[правіць | правіць зыходнік]Пункт спынення (англ.: breakpoint) — перарыванне выканання праграмы пры дасягненні пэўнага адрасу.

У ранніх працэсарах x86 для арганізацыі пункта спынення, было патрэбна замяніць першы байт каманды на каманду выкліка адладкавага перапынення (int 3), выклік перапынення вяртаў кіраванне адладчыку, які вяртаў зыходнае значэнне першага байта каманды. Акрамя таго, пункты спынення такога роду было немагчыма ўсталёўваць у ПЗП. i386 падтрымлівае такія пункты спынення для сумяшчальнасці.

Пункты спынення i386 вызначаюцца адрасам у рэгістрах адладкі. Апрацоўнік адладкі выклікаецца калі адрас наступнай каманды супадае з адрасам у рэгістры. У сувязі з тым, што такія пункты спынення не патрабуюць запісу ў памяць, яны могуць выкарыстоўвацца для адладкі праграм у ПЗП. i386 дазваляе ўсталёўваць адначасова да чатырох пунктаў спынення.

Пункты спынення i386 таксама могуць быць пазначаны на запыт (чытання ці запісу) да зменнай па зададзенаму адрасу ў памяці. Працэсар выклікае апрацоўнік адладкі пры звяртанні каманды да памяці да пэўнага адрасу.

Пастка пераключэння задачы

[правіць | правіць зыходнік]Адладкавае перапыненне можа быць выклікана пры пераключэнні на задачу (для гэтага ў сегменце стану задачы прадугледжаны адмысловы біт).

Іншыя змены

[правіць | правіць зыходнік]Лініі даных і адрасоў у працэсары 80386, як і ў працэсары 80286, не мультыплексуюцца: маецца 32 лініі даных і 32 незалежных ад іх лініі адрасу.

У складзе мікрапрацэсара маецца 8 32-бітных рэгістраў агульнага прызначэння (EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP). Малодшая 16-бітная палова кожнага з гэтых рэгістраў адпавядае рэгістрам AX, BX, CX, DX, SI, DI, BP, SP папярэдніх працэсараў сямейства x86. Як і раней, магчыма адрасацыя малодшых і старэйшых 8-бітных паловаў, малодшай 16-бітнай паловы 32-разрадных рэгістраў даных (AL і AH, BL і BH, CL і CH, DL і DH). Рэгістр-указнік каманды і рэгістр флагаў таксама сталі 32-бітнымі (EIP і EFLAGS адпаведна), прычым у рэгістры флагаў дадана новая група бітаў. Да чатырох 16-бітных сегментных рэгістраў (ES, CS, SS, DS) дадано яшчэ два 16-бітных рэгістры (FS і GS), у выніку стала 6 сегментных рэгістраў. Дададзены некалькі новых груп рэгістраў (кожны рэгістр памерам 32 біты): 3 рэгістры кіравання (CR0 (MSW), CR2, CR3), 8 рэгістраў адладкі (DR0, DR1, DR2, DR3, DR6, DR7), 2 тэставых рэгістры (TR6, TR7).

Набор інструкцый

[правіць | правіць зыходнік]Набор інструкцый i386 быў пашыраны, галоўным чынам, за конт дадання 32-бітных варыянтаў існых інструкцый (створаных 32-бітнымі прэфіксамі), уключаючы тыя ў якіх 32-бітныя варыянты маюць іншыя мнемонікі (pushad/popad, pushfd/popfd, cwd*/cdq, movsd/cmpsd/scasd/lodsd/insd/outsd, iretd), а таксама каманды mov для новых рэгістраў. Іншыя новыя інструкцыі:

- усталёўка байта паводле ўмовы (set*)

- каманды пераходаў (jmp, j*) з адносным 16-бітным зрушэннем

- каманды загрузкі поўнага адрасу для новых сегментных рэгістраў (lfs, lgs)

Сярэдняя даўжыня інструкцыі складае 3,2 байта.

Як і ў выпадку звязкі 80286-80287, абмен данымі працэсара 80386 з яго супрацэсарам ішоў праз парты з адрасамі 0F0H-0FFH, і невялікім дадаткам схемы была магчымасць далучыць супрацэсар 80287 да працэсара 80386DX[3][4], гэта прапаноўвалася ў якасці таннай альтэрнатывы выкарыстанню супрацэсара 80387.

Адмыслова для мікрапрацэсараў Intel 80386 былі распрацаваны матэматычныя супрацэсары 387SX і 387DX, аб’яднаныя адзіным імем Intel 80387. Гэтыя супрацэсары сумяшчальныя з працэсарамі 386SX і 386DX адпаведна; так, супрацэсар 387DX можна далучыць да 32-разраднай шыны працэсара. У астатнім абедзве мадэлі аналагічныя матэматычнаму супрацэсару 80287, які таксама можна выкарыстоўваць разам з працэсарам 80386.

Мадэлі

[правіць | правіць зыходнік]З 1985 года было прэзентавана мноства мадыфікацый працэсара i386, якія адрозніваліся паміж сабой прадукцыйнасцю, спажыванай магутнасцю, раздымамі і карпусамі і іншымі характарыстыкамі.

386DX

[правіць | правіць зыходнік]Першы працэсар сямейства 386 выпушчаны 13 кастрычніка 1985 года і меў тактавую частату 16 МГц. Пасля выпуску працэсараў 386SX прылады гэтай серыі атрымалі індэкс ‘’DX’’ — ‘’D’’ouble-word e’’X’’ternal, што ўказвала на яго 32-разрадную вонкавую шыну. Працэсар пазіцыянаваўся як прадукцыйнае рашэнне для настольных сістэм. Вырабляўся працэсар паводле CHMOS IV тэхналогіі і спажываў 400 мА, што значна менш за Intel 8086. 16 лютага 1987 года анансавана мадэль з частатой 20 МГц; 4 красавіка 1988 года мадэль з частатой 25 МГц і 10 красавіка 1989 года з частатой 33 МГц. Працэсар выпускаўся ў карпусах PQFP-132 (такія працэсары мелі прэфікс «NG» у назве, напрыклад, NG80386DX25) альбо ў керамічным PGA-132 (такія працэсары мелі прэфікс «A» у пачатку назвы, напрыклад, A80386DX25)

Першыя працэсары 386DX мелі памылку, якая часам прыводзіла да памылковых вынікаў пры рабоце з 32-разраднымі лікамі ў такіх праграмах, як OS/2 2.x, UNIX/386, альбо Windows у пашыраным рэжыме. Памылка прыводзіла да таго, што сістэма завісала. З прычыны некаторых праблем, у тым ліку з-за адсутнасці 32-бітных аперацыйных сістэм выправіць памылку атрымалася толькі ў красавіку 1987 года. Ужо выпушчаныя працэсары прайшлі праверку, у выніку якой працэсары, якія не мелі памылкі, былі маркіраваны двайным сімвалам «сігма» альбо адным сімвалам «IV».

386SX

[правіць | правіць зыходнік]Першая мадэль гэтага сямейства была прэзентавана 16 чэрвеня 1988 года і мела тактавую частату 16 МГц, пазней былі прэзентаваны і больш хуткія мадэлі: 20 МГц (25 студзеня 1989 года), 25 МГц і 33 МГц (абодва працэсары прэзентаваны 26 кастрычніка 1992 года). Працэсары пазіцыніяваліся як рашэнні для настольных ПК пачатковага ўзроўню і партатыўніх ПК. Сямейства SX адрозніваліся ад сямейства DX тым, што ў яго разраднацсь вонкавай шыны даных складала 16 біт, а разраднацсь вонкавай шыны адраса 24 біты. У выніку працэсар мог адрасаваць толькі 16 Мбайт фізічнай памяці, што рабіла вылічальныя сістэмы на яго аснове апаратна сумяшчальнымі з папярэднімі працэсарамі Intel 80286. У той жа час працэсар 386SX мог выконваць усе праграмы, напісаныя для 386DX і гэта рабіла яго папулярным для вырабу «Турба-плат», напрыклад, Cumulus 386SX, Intel InBoard ці Orchid Tiny Turbo.

У рамках серыі SX былі выпушчаны працэсары з маркіроўкамі 80386SXTA, 80386SXSA, 80386SXLP, якія ўяўлялі сабой убудавальныя (embedded) працэсары (серыя SXSA), працэсары малога спажывання (Low Power), а таксама ўжываліся ў іншых мэтах.

386SL

[правіць | правіць зыходнік]Першая мадэль гэтага сямейства была прэзентавана 15 кастрычніка 1990 года і мела частату 20 МГц, пазней была прэзентавана мадэль 25 МГц (30 верасня 1991 года). Працэсары пазіцыянаваліся як першыя энэргаэфектыўныя мікрапрацэсары, адмыслова прызначаныя для партатыўных ПК. Сямейства SL адрознівалася ад SX тым, што мела на крышталі таксама кантролер аператыўнай памяці, кантролер вонкавай кэш-памяці аб'ёмам ад 16 да 64Кбайт і кантролер шыны.

386EX

[правіць | правіць зыходнік]З’яўляецца мадыцікацыяй працэсара 386SX. Працэсар прызначаўся для ўбудавальных сістэм з высокай інтэграцыяй і малой спажыванай магутнасці. Адметныя асаблівасці гэтана працэсара — малое энэргаспажыванне, паніжанае напружанне сілкавання, змешчаны на крышталі кантролер перапыненняў, сікрасхема выбару чыпу, лічыльнікі і таймеры, логіка тэставання JTAG. Гэтая серыя працэсараў мела некалькі мадыфікацый: EXSA, EXTA, EXTB, EXTC. Максімальны спажываны працэсарамі ток складае 320 мА для серыі EXTC і 140 мА для працэсараў серыі EXTB.

Выкарыстоўваліся ў бартавым абсталяванні розных арбітальных спадарожнікаў і мікраспадарожнікаў і ў NASA-ўскім праекце FlightLinux.

-

Intel i386DX, 25 МГц

-

Intel i386EXTC, 25 МГц

-

Intel i386CXSA, 25 МГц

-

Intel i386 упакаваны фірмай IBM

-

Працэсары для upgrade (Cyrix and Texas Instruments)

Камп’ютары на базе працэсара Intel 80386

[правіць | правіць зыходнік]На базе мікрапрацэсараў 80386 фірмай IBM былі створаны персанальныя камп’ютары IBM AT 386 (сямейства PC) і IBM PS/2-80 (сямейства PS/2). У першым выкарыстоўвалася АС PC-DOS, а ў другім — OS/2.

Каманда распрацоўшчыкаў

[правіць | правіць зыходнік]- John Crawford, галоўны архітэктар

- Jim Slager, галоўны інжынер

- Patrick Gelsinger

- Khaled El-Ayat

- Riaz Haq

- Gene Hill

- Jan Wiliam L. Prak

- David Vannier

- Joseph «Chip» Krauskopf

- Ken Shoemaker

- Paul Ries

- Saurabha Radhika

Тэхнічныя характарыстыкі розных мадэляў

[правіць | правіць зыходнік]Звесткі, агульныя для ўсіх мадэляў

[правіць | правіць зыходнік]- Разраднасць рэгістраў: 32

- Аб'ём віртуальнай адрасаванай памяці: 64 Тбайт

- Максімальны аб'ём сегмента: 4 Гбайт[5]

| Характарыстыка, параметр | 386DX | 386SX | 386SL | 386EX |

|---|---|---|---|---|

| Дата анонсу першай мадэлі | 13 кастрычніка 1985 года | 16 чэрвеня 1988 года | 15 кастрычніка 1990 года | жнівень 1994 года |

| Тактавыя частоты (МГц) | 16, 20, 25, 33, 40 | 12(серыя SXSA), 16, 20, 25, 33, 40(серыі SXSA і SXTA) | 20, 25 | 16, 20, 25, 33 (магчыма існавалі і іншыя мадэлі) |

| Разраднасць вонкавай шыны даных | 32 біт | 16 біт | 16 біт | 16 біт |

| Разраднасць вонкавай шыны адрасу | 32 біт | 24 біт | 24 біт | 26 біт |

| Аб'ём фізічнай адрасаванай памяці | 4 ГБ | 16 Мбайт | 16 Мбайт | 64 Мбайт (для серый EXTB, EXTC) |

| Напружанне сілкавання, вольт | 5 | 5 | 5 | 2,7~3,6 В (серыя EXTB) 4,5~5,5В (серыя EXTC) |

| Колькасць транзістараў | 275 000 | 275 000 | 855 000 | 275 000 |

| Тэхпрацэс (нм) | 1500 і 1000 (мадэль 33 МГц) | 1500 і 1000 | 1000 | 800 |

| Плошча крышталя | 42 мм² (для мадэлі 33 МГц) | няма звестак | няма звестак | няма звестак |

| Максімальны спажываны ток | 0,39 А (мадэль 33 МГц) | 0,38 А (мадэль 33 МГц) | няма звестак | няма звестак |

| Максімальная спажываная магутнасць, Вт | 1,95 (мадэль 33 МГц) | 1,9 (мадэль 33 МГц) | няма звестак | няма звестак |

| Раздым | Гняздо тыпу «Socket» альбо прыпайваўся да платы | Працэсар прыпайваўся да платы | Працэсар прыпайваўся да платы | Працэсар прыпайваўся да платы |

| Корпус | 132-кантактны керамічны PGA, альбо 132-контактный PQFP | 100-кантактны PQFP | 196-кантактны PQFP | 132-кантактны PQFP, 144-кантактны TQFP |

| Набор інструкцый | x86 (150 інструкцый, не лічачы мадыфікацый) | x86 (150 інструкцый, не лічачы мадыфікацый) | x86 | x86 |

Зноскі

- ↑ Intel cashes in ancient chips (англ.)(недаступная спасылка). Архівавана з першакрыніцы 22 жніўня 2011. Праверана 10 красавіка 2010.

- ↑ Product Change Notification #106013 - 00(недаступная спасылка). Архівавана з першакрыніцы 11 студзеня 2012. Праверана 13 лістапада 2014.

- ↑ краткое описание 80287 на cadcenter Архівавана 26 красавіка 2008.

- ↑ BootPrompt-HOWTO в Linux: «Параметр загрузки ядра 'no387': В некоторых сопроцессорах i387 есть ошибки, вылезающие в 32-битовом защищенном режиме. Например, некоторые ранние чипы ULSI-387 вызывают жесткое зависание при вычислениях с плавающей запятой, очевидно из-за ошибки в командах FRSAV/FRRESTOR. Параметр загрузки `no387' позволяет Linux игнорировать мат. сопроцессор, даже если он имеется. Конечно, у вас тогда должно быть ядро с поддержкой математической эмуляции. Это может быть также полезным, если у вас действительно одна из старых 386 машин с 80287 FPU, так как Linux не может использовать 80287.»; оригинал на английском

- ↑ Intel 80386 - www.lycos.com (англ.). Архівавана з першакрыніцы 22 жніўня 2011. Праверана 10 красавіка 2010.

Літаратура

[правіць | правіць зыходнік]- Intel 80386 Programmer’s Reference Manual

- Intel 80387 Programmer’s Reference Manual (1987 год)

Спасылкі

[правіць | правіць зыходнік]- Апісанне і фатаграфіі працэсараў сямейства i386 (англ.)

- Дакументацыя на працэсар Архівавана 28 ліпеня 2014. на сайце bitsavers.org (англ.)

- Краткое описание микропроцессора Intel 80386 Архівавана 16 лютага 2012. (руск.)