Intel 80486

| Production | De 10 avril 1989 à 28 septembre 2007 |

|---|---|

| Concepteur | Intel |

| Fabricant | Intel, IBM, AMD, Texas Instruments |

| Fréquence | 16 MHz à 100 MHz |

|---|---|

| Fréquence du FSB | 16 MT/s à 50 MT/s |

| Largeur bus données | 32 bits |

| Largeur bus adresse | 32 bits |

| Largeur bus adresse virtuelle |

32 bits (linéaire) 46 bits (logique) |

| Niveau 1 | 4 ou 8 ko unifié |

|---|

| Finesse de gravure | 1 µm à 0,6 µm |

|---|---|

| Nombre de transistors | 1,2[1] – 1,6 million |

| Socket(s) |

| Architecture | x86-16, IA-32 y compris x87 (sauf pour les modèles "SX") |

|---|

| Variantes |

|---|

L'Intel 80486 (i486, 486) est un microprocesseur de la famille des x86, fabriqué par Intel. Il est lancé en 1989.

Du point de vue de l'architecture de processeur, le 80486 est très semblable à son prédécesseur immédiat, l'Intel 80386, avec l'ajout de quelques instructions supplémentaires. C'est donc une architecture CISC.

Du point de vue de la microarchitecture, c'est une grande amélioration. Il y a une mémoire cache unifiée intégrée d'instructions et de données, en option une unité de calcul en virgule flottante (FPU) intégrée, et une unité d'interface de bus améliorée. En outre, dans des conditions optimales, le cœur du processeur peut soutenir un rythme d'exécution d'une instruction par cycle. Ces améliorations permettent approximativement de doubler la vitesse d'exécution par rapport à un 80386 à la même fréquence de base. Cependant, quelques modèles bas de gamme (Intel 80486SX) sont plus lents que les 80386 les plus rapides.

Une version 25 MHz est présentée en avril 1989, une version 33 MHz en mai 1990, et une version 50 MHz en juin 1991.

Il existe plusieurs suffixes et variantes comprenant :

- Intel 80486DX - le 80486 original, avec un coprocesseur mathématique (FPU) intégré ;

- Intel 80486SX - un 80486DX sans FPU ; les premières versions sont en fait des 80486DX dont le FPU est défectueux et donc neutralisé ; dans les versions postérieures, le FPU est retiré de la puce pour réduire sa taille, et donc son coût ;

- Intel 80486DX2 - l'horloge interne du processeur tourne à deux fois la fréquence de base de l'horloge du bus externe ;

- Intel 80486SX2 - le même que le 80486DX2, mais avec le FPU neutralisé ;

- Intel 80486SL - 80486DX avec des circuits de gestion d'alimentation, principalement utilisé dans les ordinateurs portables ;

- Intel 80486SL-80486SL-NM - 80486SX avec des circuits de gestion d'alimentation ;

- Intel 80487 - 80486DX avec un plan de brochage légèrement différent pour être utilisé comme FPU dans les systèmes 80486SX ;

- Intel 80486 OverDrive (en) - 80486SX, 80486SX2, 80486DX2 ou 80486DX4 - marqués comme processeurs de mise à niveau, quelques modèles ont des plans de brochages ou des tensions différentes des processeurs équivalents standards ;

- Intel 80486DX4 - conçu pour tourner à trois fois la fréquence de base du bus externe (non quadruple comme souvent cru).

Les fréquences du bus externe sont 16 MHz, 20 MHz, 25 MHz, 33 MHz, 40 MHz et 50 MHz. Plus tard, quelques cartes mères 80486 permettent le support officieux et non documenté des 60 et 66 MHz.

Améliorations par rapport au 80386

[modifier | modifier le code]

Le jeu d'instructions du i486 est très similaire à celui du i386, avec l’ajout de quelques instructions supplémentaires, telles que CMPXCHG, une opération atomique de comparaison et d'échange, et XADD, une opération atomique de récupération et d'ajout qui renvoie la valeur d’origine (contrairement à un ADD standard, qui renvoie uniquement des drapeaux). Cette génération de processeur comprend jusqu’à 156 instructions différentes[2].

L’architecture de l’i486 est une grande amélioration par rapport à celle de l'i386. Il dispose d’un cache d’instructions et de données unifié sur puce, d’une unité de calcul en virgule flottante (FPU) sur puce et d’une unité d’interface de bus améliorée[3]. En raison de l’étroitesse du pipeline, des séquences d’instructions simples (telles que ALU reg,reg et ALU reg,im) pouvaient maintenir un débit d’un cycle d’horloge unique (une instruction exécutée à chaque cycle). En d’autres termes, il fonctionnait à environ 1,8 cycles d'horloge par instruction[4]. Ces améliorations ont permis de doubler grossièrement les performances ALU entières par rapport à l’i386 à la même fréquence d’horloge. Un i486 à 16 MHz avait donc des performances similaires à celles d’un i386 à 33 MHz. Avec la combinaison du processeur et du co-processeur sur la puce, le taux d’utilisation du bus serait de 50 % pour la version Intel 486 à 25 MHz[5]. En d’autres termes, la combinaison du processeur et du MCP (coprocesseur mathématique) offre 40 % de performances en plus par rapport à l'Intel 386 DX combiné au coprocesseur mathématique Intel 387 DX[6]. L’ancienne conception devait atteindre 50 MHz pour être comparable à un i486 à 25 MHz[note 1].

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Différences entre i386 et i486

[modifier | modifier le code]- Un cache SRAM sur puce (niveau 1) de 8 Ko stocke les instructions et les données les plus récemment utilisées (16 Ko et/ou en écriture différée sur certains modèles ultérieurs). Le i386 n’avait pas de cache interne mais supportait un cache hors puce plus lent (pas réellement un cache de niveau 2 car le i386 n’avait pas de cache interne de niveau 1).

- Un protocole de bus externe amélioré pour permettre la cohérence du cache et un nouveau mode en rafale pour les accès à la mémoire afin de remplir une ligne de cache de 16 octets en cinq cycles de bus. Le 386 avait besoin de huit cycles de bus pour transférer la même quantité de données.

- Le pipeline étroitement couplé[note 2] exécute une instruction simple comme ALU reg,reg or ALU reg,im à chaque cycle d’horloge (après une latence de plusieurs cycles). Le i386 avait besoin de deux cycles d’horloge.

- FPU intégré (désactivé ou absent sur les modèles SX) avec un bus local dédié ; associé à des algorithmes plus rapides sur un matériel plus complet que dans l’i387, il effectuait des calculs en virgule flottante plus rapidement que la combinaison i386/i387.

- Amélioration des performances du MMU.

- Nouvelles instructions : XADD, BSWAP, CMPXCHG, INVD, WBINVD, INVLPG.

Tout comme dans le i386, un modèle de mémoire linéaire de 4 Go a été mis en œuvre. Tous les registres du « sélecteur de segments » peuvent être définis sur une valeur neutre en mode protégé, ou sur zéro en mode réel, et en utilisant uniquement les « registres d'offset » de 32 bits (terminologie x86 pour les registres généraux du processeur utilisés comme registres d’adresses) comme une adresse virtuelle linéaire de 32 bits en contournant la logique de segmentation. Les adresses virtuelles sont alors normalement mappées sur des adresses physiques par le système de pagination, sauf lorsqu’il est désactivé (le mode réel n’a pas d’adresses virtuelles). Tout comme avec l'i386, le contournement de la segmentation de la mémoire peut améliorer considérablement les performances de certains systèmes d’exploitation et applications.

Sur une carte mère de PC typique, quatre SIMM à 30 broches (8 bits) appariés ou un SIMM à 72 broches (32 bits) par banque étaient nécessaires pour s’adapter au bus de données 32 bits de l'i486. Le bus d’adresses utilisait 30 bits (A31.. A2) complété par quatre broches de sélection d’octets (au lieu de A0, A1) pour permettre toute sélection de 8/16/32 bits. Cela signifiait que la limite de la mémoire physique directement adressable était également de 4 gigaoctets (230 mots de 32 bits = 232 mots de 8 bits).

Galerie

[modifier | modifier le code]-

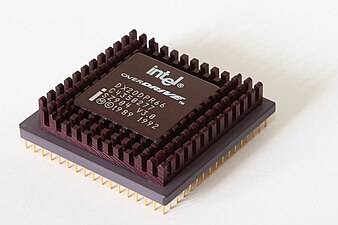

Intel 80486DX2 66 MHz

-

Intel 80486DX2 Overdrive

-

Intel 486DX2 50 MHz @ 3,3 V (cache 8 ko). Cette puce, basée sur la microarchitecture 80486, disposait d'un doubleur de fréquence d'horloge fonctionnant à 50 MHz. Elle comprend l'unité de calcul en virgule flottante.

Note et références

[modifier | modifier le code]Notes

[modifier | modifier le code]- ↑ Les processeurs pre-DX2 i486 ne possédaient pas de multiplicateur d'horloge et sont donc comparables à un 386/286 à fréquence d'horloge double.

- ↑ Les 386, 286 et même le 8086 avaient tous des étapes de chargement, de décodage, d'exécution (calcul) de l'instruction et d'écriture des résultats se chevauchant ; cependant, un pipeline étroitement couplé signifie habituellement que tous les étages effectuent leurs tâches respectives pendant la même tranche de temps. Par contraste, un pipeline faiblement couplé signifie qu'une forme de tampon est utilisée pour découpler les unités et leur permettre de fonctionner plus indépendamment. Le 8086 original et les puces x86 actuelles sont sur ce point "faiblement couplés", tandis que le i486 et le Pentium original fonctionnaient de manière "étroitement couplée" pour les instructions typiques. Celles-ci comprenaient la plupart des instructions de type "CISC" ainsi que les instructions simples de type "RISC" sans load/store, bien que les plus complexes utilisent également un pilotage par microcode dédié.

Références

[modifier | modifier le code]- ↑ (en)Lewnes, Ann, "The Intel386 Architecture Here to Stay", Intel Corporation, Microcomputer Solutions, July/August 1989, page 2

- ↑ (en)House, Dave, "Putting the RISC vs. CISC Debate to Rest", Intel Corporation, Microcomputer Solutions, November/December 1991, page 18

- ↑ (en) Cet article contient des extraits de la Free On-line Dictionary of Computing qui autorise l'utilisation de son contenu sous licence GFDL.

- ↑ (en)Chen, Allan, "Designing A Mainframe on a Chip: Interview with the i486 Microprocessor Design Team", Intel Corporation, Microcomputer Solutions, July/August 1989, page 12

- ↑ (en)Intel Corporation, "Coming Attractions: Clock-Doubling Technology", Microcomputer Solutions, January/February 1992, page 6

- ↑ (en)Intel Corporation, "A Guide to the Intel Architecture", Microcomputer Solutions, January/February 1992, page 11